Микропроцессорная архитектура. Архитектура микропроцессора основные характеристики микропроцессора

Особенности архитектуры современных МП

Одной из основных характеристик МП является тип его архитектуры.

К архитектуре микропроцессора относят систему команд и способы адресации, возможность совмещения выполнения команд во времени, наличие дополнительных устройств в составе микропроцессора, принципы и режимы его работы и др.

При попытке классифицировать архитектуры современных микропроцессоров, неизбежно возникает проблема, связанная со стремительным и бурным развитием технологий их производства. На каждом этапе развития микропроцессоров в силу различных возможностей элементной базы и предпочтений фирм-производителей доминирует определенная взаимосвязанная совокупность архитектурных идей. В дальнейшем эти идеи могут быть скомбинированы с другими, и представлять собой уже иную архитектуру. В силу указанных причин, предлагаемая ниже классификация не в полной мере будет отражать современный уровень развития архитектур МП.

Под архитектурой МП принято понимать совокупность представлений о составе его компонентов, организации обмена информацией внутри МП и с внешней средой, реализуемых системой команд.

Выделяют понятия:

Микроархитектура;

Макроархитектура

Микроархитектура микропроцессора - это аппаратная организация и логическая структура микропроцессора, регистры, управляющие схемы, арифметико-логические устройства, запоминающие устройства и связывающие их информационные магистрали.

Макроархитектура - это система команд, типы обрабатываемых данных, режимы адресации и принципы работы микропроцессора.

В целом, архитектуру микропроцессора можно классифицировать по следующим признакам.

1. По количеству обрабатываемых потоков данных

По количеству обрабатываемых потоков данных все существующие микропроцессоры условно можно разделить на три класса.

Первыми двумя являются микропроцессоры с векторно-конвейерной архитектурой и ассоциативные процессоры с SIMD-архитектурой (Single Instruction-Multiple Data). В этих МП все обрабатывающие процессорные элементы выполняют команды одного потока, выдаваемые одним общим устройством управления. По большому счету, все ниже рассматриваемые архитектуры относятся именно к SIMD-архитектуре.

К третьему классу МП, выделяемых по данному признаку классификации, можно отнести мультипроцессорные системы с архитектурой MIMD (Multiple Instruction-Multiple Data). Такая архитектура обрабатывает одновременно много потоков данных множеством потоков команд.

2. По решаемым задачам:

По решаемым задачам различают регистровую архитектуру микропроцессора,стековую архитектуру микропроцессора, архитектурумикропроцессора, ориентированную на оперативную память.

Регистровая архитектура микропроцессора (архитектура типа «регистр регистр») − определяет наличие достаточно большого регистрового файла внутри БИС микропроцессора. Этот файл образует поле памяти с произвольной записью и выборкой информации. Микропроцессоры с регистровой архитектурой имеют высокую эффективность решения научно-технических задач. Это связано с высокой скоростью работы сверхоперативного ОЗУ (СОЗУ), которое позволяет эффективно использовать скоростные возможности арифметико-логического блока. Однако при переходе к решению задач управления эффективность таких микропроцессоров падает, так как при переключениях программ необходимо разгружать и загружать регистры СОЗУ.

Стековая архитектура микропроцессора − дает возможность создать поле памяти с упорядоченной последовательностью записи и выборки информации. Эта архитектура эффективна для организации работы с подпрограммами, что необходимо для решения сложных задач управления, или при работе с языками высокого уровня. Хранение адресов возврата позволяет организовать в стеке эффективную обработку последовательностей вложенных подпрограмм. Однако стек на кристалле микропроцессора с малой информационной емкостью быстро переполняется, а стек большой емкости требует значительных ресурсов. Реализация стека в ОЗУ решает эти проблемы.

Архитектура микропроцессора, ориентированная на оперативную память (архитектура типа «память память») − обеспечивает высокую скорость работы и большую информационную емкость рабочих регистров и стека при их организации в ОЗУ. Эта архитектура отнесена к типу «память память», поскольку в МП с такой архитектурой все обрабатываемые числа после операции в микропроцессоре вновь возвращаются в память, а не хранятся в рабочих регистрах.

Наибольшее распространение получила именно последняя архитектура. Особенно это относится к системам, работающим в реальном масштабе времени и к системам обработки данных, ориентированных на использование в системах управления.

3. По типу обрабатываемых команд.

По типу обрабатываемых команд выделяют два класса - RISC (Reduce Instruction Set Computer) архитектура МП с скоращенным набором команд и CISC (Complete Instruction Set Computer) архитектура МП с расширенным набором команд . К этому признаку можно отнести и архитектуру EPIC (Explicitly Parallel Instruction Computing) - архитектуру с вычислениями с явным параллелизмом команд.

Критерием оптимизации системы команд первых процессоров была минимизация длины программ для решения требуемых задач. При этом вводились команды, которые использовали в качестве операндов как регистры и ячейки памяти, так и сложные схемы формирования адресов с использованием индексных регистров. Набор команд ограничивался форматами «регистр регистр, регистр», «память регистр» и «регистр память». В связи со сказанным и с тем, что компиляторы не в состоянии эффективно использовать сложные команды формировалась концепция процессоров с сокращенным набором команд - RISC-процессоров. Появлению RISC-процессоров так же способствовали особенности архитектуры конвейерных процессоров: наличие отдельных наборов команд для работы с памятью и отдельных наборов команд для преобразования информации в регистрах процессора. Каждая такая команда единообразно разбивается на небольшое количество этапов с одинаковым временем исполнения (выборка команды, дешифрация команды, исполнение, запись результата). Это, в свою очередь, позволяет построить эффективный конвейер процессора, способный каждый такт выдавать результат исполнения очередной команды.

Основными чертами RISC-концепции являются:

– одинаковая длина команд;

– одинаковый формат команд;

– операндами команд могут быть только регистры;

– команды выполняют только простые действия;

– наличие большого количества регистров общего назначения (РОН) (РОН могут быть использованы любой командой);

– наличие конвейеров;

– выполнение команды не дольше, чем за один такт;

– простая адресация.

К RISC процессорам относятся процессоры архитектуры MIPS, SPARC, PowerPC, DEC Alpha, HP PA-RISC, Intel 960, AMD 29000 и др.

Очевидно, что RISC-процессоры эффективны там, где можно продуктивно использовать структурные способы уменьшения времени доступа к оперативной памяти. Если программа генерирует произвольные последовательности адресов обращения к памяти и каждая единица данных используется только для выполнения одной команды, то фактически производительность процессора определяется временем обращения к основной памяти. В этом случае использование сокращенного набора команд только ухудшает эффективность, и более оптимальными, с точки зрения производительности, являются CISC-процессоры.

В отличии от RISC-процессоров, в CISC-процессорах, как правило, команды имеют много разных форматов и требуют для своего представления различного числа ячеек памяти. Это обусловливает определение типа команды в ходе ее дешифрации при исполнении, и, в целом, усложняет устройство управления процессора и препятствует повышению тактовой частоты до уровня, достижимого в RISC-процессорах на той же элементной базе. В наборе команд CISC часто присутствуют, например, команды организации циклов, команды вызова подпрограммы и возврата из подпрограммы, сложная адресация, позволяющая реализовать одной командой доступ к сложным структурам данных. Основной недостаток CISC - большая сложность реализации процессора при малой производительности. Примеры CISC процессоров - семейство Motorola 680x0 и процессоры фирмы Intel от 8086 до Pentium 4.

Несмотря на указанные недостатки, в настоящее время на рынке МП доминируют CISC-процессоры. Это связано с тем, что развитие микропроцессоров происходит при постоянном стремлении сохранения преемственности программного обеспечения (ПО).

Однако, сохранение преемственности ПО и существующее требование повышения производительности МП противоречат друг другу. Для разрешения данного противоречия ведущими производителями МП была реализована успешная попытка решения проблемы повышения производительности в рамках CISC-архитектуры. Сохраняя преемственность по системе команд с CISC-микропроцессорами, разработчики создали новые устройства с использованием элементов RISC-архитектуры. В микропроцессор встраивается аппаратный транслятор, превращающий команды CISC-микропроцессора в команды внутреннего RISC-процессора. При этом одна команда из сложного набора может порождать до четырех команд RISC-процессора. Характерным примером таких «смешанных» МП являются последние МП фирмы AMD и фирмы Intel.

В настоящее время, по заявлениям разработчиков - фирм Intel и Hewlett-Packard, архитектурой той же значимости, что CISC и RISC является EPIC архитектура.

Особенностями EPIC архитектуры являются:

– большое количество регистров; масштабируемость архитектуры до большого количества функциональных устройств;

– явный параллелизм в машинном коде; поиск зависимостей между командами производит не процессор, а компилятор;

– предикация (Predication) - команды из разных ветвей условного ветвления снабжаются предикатными полями (полями условий) и запускаются параллельно;

К процессорам с EPIC-архитектурой относят Merced, работы над которым вела фирма Intel и McKinley, который разрабатывался в HP.

4. По виду исполняемых команд.

По виду исполняемых команд различают скалярные процессоры и векторные процессоры.

Классификация по данному признаку находит своё обоснование по типу исполняемых команд. Если входными операндами команды МП и её результат являются целочисленные операнды или операнды с плавающей точкой (скаляры) то такой МП относят к классу скалярных МП . При этом в МП предусмотрено более одного конвейера, позволяющего одновременно выполнять более одной разной инструкции (команды). Впервые реализована в МП Pentium (2 конвейера из 5 стадий каждый), у МП Pentium Prо уже 3 конвейера.

Если входные операнды обрабатываемой команды МП и, возможно, результат являются вектором (массивом) чисел, то такой МП является векторным (или векторно-конвейерным) . Появление векторных команд и, соответственно, векторных процессоров, обусловлено стремлением ускорить обработку массивов данных за счёт исключения затрат времени на выборку и дешифрацию команд обработки, одинаковых для всех компонентов входных массивов.

5. По возможности параллельной обработки данных.

По возможности параллельной обработки данных выделяют суперскалярные, с длинным словом команды (VLIW), мультитредовые микропроцессоры.

Современные микропроцессоры содержат десять и более обрабатывающих устройств, каждое из которых представляет собой конвейер. В случае эффективной загрузки параллельно функционирующих устройств возможно получение в одном такте нескольких результатов операций, представленных скалярами.

Эффективная загрузка параллельно функционирующих конвейеров обеспечивается либо аппаратурой процессора, либо компилятором, либо совместно аппаратурой и компилятором. В компиляторах используется изощренная техника извлечения параллелизма из последовательных программ. Аппаратура микропроцессоров ориентирована на выделение более простых форм параллелизма, в том числе естественного.

При отображении внутреннего параллелизма обработки данных микропроцессора на архитектурном уровне в системе команд выделяют два крайних подхода.

Первый подход состоит в том, что никакого указания на параллельную обработку внутри процессора система команд не содержит. Такие процессоры относятся к классу суперскалярных . Такое название, с одной стороны, отличает эти процессоры от векторных процессоров, а с другой стороны, подчеркивает присущий этим процессорам внутренний параллелизм, обеспечивающий получение в одном такте нескольких скалярных результатов.

В отличии от скалярных МП в данной архитектуре предусмотрен дополнительно хотя бы один конвейер, включающий на одной из стадий несколько параллельных исполнительных блоков, осуществляющих «спекулятивное» исполнение инструкции.

В суперскалярных процессорах в рамках модели последовательных программ реализуется параллельное исполнение команд этих программ. После извлечения последовательного потока команд между командами устанавливаются только действительно необходимые зависимости по данным. При этом, чтобы сохранить порядок при наступлении прерывания, сохраняется достаточно информации о очередности следования команд в исходной программе.

Типичный суперскалярный процессор выбирает команды и исследует их по мере выполнения. Это действие проводится с целью выявления и обработки команд перехода, идентификации типа команды для ее дальнейшего направления на соответствующий исполнительный блок или в буфер памяти. Эффективность использования суперскалярных архитектур, как правило, ограничивается наличием в программах условных переходов. Это приводит к резкому возрастанию требований к ресурсам и ограничивает количество исполняемых команд. Считается, что пределом распараллеливания при суперскалярной обработке является запуск одновременно на исполнение в каждом такте 7- 8 команд.

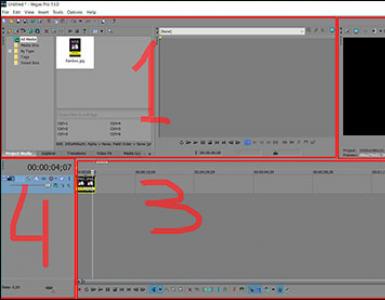

Рис. 12.1 Структура суперскалярного микропроцессора

На рисунке 12.1 показаны основные компоненты суперскалярного микропроцессора. Функциональными модулями такого МП являются модули выполнения операций с плавающей точкой (FPU) и фиксированной точкой (ALU), устройство загрузки/сохранения, файлы регистров, раздельная кэш-память команд и данных, а так же вспомогательные модули, обеспечивающие динамическое планирование вычислительного процесса, устройство связи с кэш-памятью второго уровня, блок переупорядочивания команд и блок предварительной дешифрации.

Второй подход к отображению присущего микропроцессору внутреннего параллелизма обработки данных на архитектурном уровне в системе команд полностью открывает пользователю все возможности параллельной обработки. В специально отведенных полях команды каждому из параллельно работающих обрабатывающих устройств предписывается действие, которое устройство должно совершить. Такие процессоры называются процессорами с длинным командным словом (VLIW) .

Достоинства VLIW заключаются в следующем. Во-первых, компилятор может более эффективно исследовать зависимости между командами и выбирать параллельно исполняемые команды, чем это делает аппаратура суперскалярного процессора, ограниченная размером окна исполнения.

Во-вторых, VLIW-процессор имеет более простое устройство управления и потенциально может иметь более высокую тактовую частоту.

Однако у VLIW-процессоров есть серьезный фактор, снижающий их производительность. Это команды ветвления, зависящие от данных, значения которых становятся известны только в динамике вычислений.

Очередь команд VLIW-процессора не может быть очень большой ввиду отсутствия у компилятора информации о зависимостях, формируемых динамически, в процессе выполнения. Этот недостаток препятствует возможности переупорядочивания операций в VLIW-процессоре. Кроме того, такой процессор требует большого размера памяти имен, многовходовых регистровых файлов, большого числа перекрестных связей. Возможен также останов, когда во время выполнения возникла ситуация, отличающаяся от состояния в момент генерации плана выполнения (например, во время выполнения произошло неудачное обращение в кэш).

Суперскалярные микропроцессоры и микропроцессоры с длинным командным словом имеют один счетчик команд и, в силу этого, могут быть названы однотредовыми. Такой подход ограничивает производительность вычислительной структуры.

Дальнейшее повышение производительности МП в настоящее время связывается со статическим и динамическим анализом кода с целью выявления параллелизма уровня программных сегментов. При этом, для параллельного исполнения команды одной или нескольких программ, в микропроцессор вводится несколько счетчиков команд и другое дополнительное оборудование. Такие микропроцессоры с несколькими счетчиками команд получили название мультитредовые.

Мультитредовая архитектура решает проблему борьбы с простоями функциональных устройств процессора, возникающими из-за невозможности выполнения следующей команды. Это достигается путем переключения на другой регистровый файл. В результате процессор получает другие данные для продолжения вычислений, переходя к выполнению другого треда (процесса).

Мультитредовый процессор может исполнять процессы, принадлежащие одной или нескольким программам. Если процессор исполняет одну программу, то говорят о его производительности, если несколько программ - о пропускной способности.

В результате применения таких процессоров производительность МП, при прочих равных условиях, может возрасти в десятки раз.

6. По виду используемой памяти (по количеству используемых шин).

По виду используемой памяти различают Принстонскую архитектуру, (архитектуру фон Неймана или одношинную архитектуру), гарвардскую архитектуру(двухшинную архитектуру), SHARC архитектуру (супергарвардскую архитектуру , с использованием специального шинного коммутатора).

Одношинная или Принстонская архитектура – архитектура с общей, единой шиной для данных и команд, а значит и одна общая память как для данных, так и для команд (рис. 12.2).

Рис. 12.2. Архитектура с общей шиной данных и команд.

Двухшинная или Гарвардская архитектура отличается наличием отдельной памяти данных и отдельной памяти команд со своими шинами (рис. 12.3).

Рис. 12.3. Архитектура с раздельными шинами данных и команд.

Архитектура с раздельными шинами данных и команд достаточно сложная, она заставляет процессор работать одновременно с двумя потоками кодов, обслуживать обмен по двум шинам одновременно. Программа может размещаться только в памяти команд, данные - только в памяти данных. Такая узкая специализация ограничивает круг задач, решаемых системой, так как не дает возможности гибкого перераспределения памяти. Память данных и память команд в этом случае имеют не слишком большой объем, поэтому применение систем с данной архитектурой ограничивается обычно не слишком сложными задачами.

Супергарвардская архитектура (SHARC) (рис. 12.4) является примером гармоничного сочетания принципов построения распределенных и связанных систем, объединяя в себе простоту и эффективность масштабирования распределенных систем с удобством программирования систем с разделяемой памятью.

В SHARC-микропроцессоре объединены высокоэффективное процессорное ядро, выполняющее обработку данных в формате с плавающей точкой, интерфейс с хост-процессором, контроллер ПДП, последовательные порты, коммуникационные линки (связи) и разделяемая шина.

Шинный коммутатор соединяет ядро процессора с независимым процессором ввода/вывода, двухвходовой памятью и портом шины мультипроцессорной системы.

Рис. 12.4. Супергарвардская архитектура (SHARC).

7. По производителю

По производителю можно выделить следующие основные классы МП:

· Микропроцессоры с архитектурой х86:

- МП компании Intel : i8086, i80286, i80386, i80486, линия Pentium (Р5), Pentium Pro (Р6) и процессоры на его основе Pentium II, Pentium III, Pentium 4 (и их упрощённый вариант Celeron), Pentium М и другие разновидности этих МП, Merced (P7) и усовершенствованные модели IA-64;

- МП компании NexGen: модели линейки Nx586, Nx686 и другие модели, выпущенные совместно с компанией AMD;

- МП компании AMD: К5, К6 (K6-II), K7 (линия Athlon (Duron)), семейство Hammer;

- МП компании Cyrix : 5х86, 6х86, 6х86МХ, и модели WinChip, WinChip2, VIA Cyrix III после слияния с компанией VIA; ;

- МП компании Transmeta: семейство Crusoe – ТМ3120, ТМ 5400, ТМ 8000 и др.;

· Микропроцессоры с архитектурой Power PC:

- МП компании Motorola и IBM : Power PC 603, 604, 620, 750/740 (G3), G4, G5, Power PC 970, Power 3, Power 4;

· Микропроцессоры с архитектурой Alpha:

- МП компании DEC: линия Alpha (21064, 21164, 21264, 21364 (компании HP)).

· Микропроцессоры с архитектурой SPARC:

- МП компании Sun Microsystems: линия SPARC (Micro SPARC, Super SPARC, Hiper SPARC и 64-разрядный МП Ultra SPARC).

· Микропроцессоры с архитектурой MAJC:

- МП компании Sun: линия MAJC (MAJC5200, MAJC5200+)

· Микропроцессоры с архитектурой PA:

- МП компании HP: PA-8000, PA-8500, PA-8700, PA-8800 (Mako), PA-8900.

· Микропроцессоры с архитектурой MIPS

- МП компании Silicon Graphics: линия MIPS R-x(R10000, R12000, R14000, R16000, R18000, R20000).

Таким образом, в настоящее время существует множество типов архитектур. Исторически архитектуры процессоров возникли исходя из предполагаемого набора задач, которые должны были исполняться на этих процессорах, и преемственности решаемых программ. Сегодня, имеющиеся аппаратные ресурсы, позволяют собрать в одном процессоре все известные архитектурные приемы повышения производительности, сообразуясь только с взаимной совместимостью. Поэтому, как считают некоторые современные ученые, скорее всего, до появления единой архитектуры процессора ещё достаточно далеко.

2. Тенденции развития современных МП

Анализ конкретных семейств микропроцессоров разных производителей подтверждает общие тенденции их развития: повышение тактовой частоты, увеличение объема и пропускной способности подсистемы памяти, увеличение количества параллельно функционирующих исполнительных устройств. Совокупная реализация в одном микропроцессоре рекордных значений по всем этим тенденциям невозможна из-за фундаментальных физических ограничений, а также из-за ограничений технологического процесса изготовления и экономических ограничений на стоимость одного микропроцессора и микроэлектронного производства в целом. Поэтому каждый конкретный тип микропроцессора есть результат многих компромиссов, принятых его создателями. Рассмотрим более подробно суть этих компромиссов на примерах сопоставительного анализа развития семейств микропроцессоров.

Эта глава посвящена архитектурным особенностям микропроцессоров. В ней приведены общие сведения о микропроцессорах, рассматриваются принципы структурно - функциональной организации) типы данных, регистровая память, спо-собы адресации и система команд микропроцессоров. Излагаемый материал ил-люстрируется на простейших 8- и 16-разрядных процессорах.

Основные понятия

Микропроцессор — это программно-управляемое устройство в виде интегральной микросхемы (БИС или СБИС), предназначенное для обработки цифровой информации. Поскольку все современные микро-процессоры имеют интегральное исполнение, синонимом микропроцессора стал термин процессор.

Микроконтроллер — это специализированный процессор, предназначен-ный для реализации функций управления (control— управление).

{xtypo_quote}Цифровой сигнальный процессор(Digital Signal Processor — DSP) — это специа-лизированный процессор, предназначенный для обработки цифровых сигналов. {/xtypo_quote}

Микропроцессорная система представляет собой функционально законченное изделие, состоящее из нескольких цифровых устройств, включая процессор. Это понятие объединяет широкий набор законченных изделий, начиная с микроконтроллеров, выполненных на интегральных микросхемах, и кон-чая компьютерными системами, представляющими собой набор отдельных конст-руктивно оформленных устройств (системный блок, клавиатура, монитор и др.). В дальнейшем рассматриваются простейшие (однокристальные) микропроцес-сорные системы, содержащие помимо процессора основную память и устройства ввода/вывода. Такие микропроцессорные системы можно отнести к классу микро-процессоров.

Под организацией процессора понимают совокупность его узлов (устройств, блоков, модулей), связи между узлами и их функциональные характе-ристики. Организация определяет аппаратную организацию процессора, т. е. состав и взаимодействие его аппаратных средств. Выделяют два уровня организации:

● физическую организацию в виде принципиальной схемы;

● логическую организацию в виде структурно-функциональной схемы.

В дальнейшем рассматривается организация микропроцессоров на логиче-ском уровне, или структурно-функциональная организация процессоров.

Под архитектурой процессора будем понимать совокупность его программно-аппаратных средств, обеспечивающих обработку цифровой инфор-мации (выполнение программы), т. е. совокупность всех средств, доступных про-грамме (или пользователю). Это более общее понятие по сравнению с понятием организация включает в себя набор программно-доступных регистров и операци-онных устройств, систему основных команд и способов адресации, объем и орга-низацию адресуемой памяти, виды и способы обработки данных (обмен, преры-вания, примой доступ к памяти и др.).

{xtypo_quote}Например, современные 32-разрядные процессоры х86 с архитектурой IA-32 (Intel Architecture — 2 bit) имеют стандарт-ный набор регистров, общую систему основных команд, одинаковые способы организации и адресации памяти, защиты памяти и обслуживания прерываний. Отметим, что понятие архитектуры в большей степени характеризует свойства системы, чем устройства. {/xtypo_quote}

Основные виды архитектур

По форматам используемых команд (инструкций) можно выделить:

● CISC-архитектуру, которая относится к процессорам (компьютерам) с полным набором команд (Complete Instruction Set Computer— CISC). Она реализова-на во многих типах микропроцессоров (например Pentium), выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации.

Система команд процессоров с CISC-архитектурой может содержать не-сколько сотен команд разного формата (от 1 до 15 байт), или степени слож-ности, и использовать более 10 различных способов адресации, что позволя-ет программисту реализовать наиболее эффективные алгоритмы решения различных задач.

Развитие традиционных CISC

Архитектур микропроцессоров по пути рас-ширения функциональных возможностей и снижения затрат на программиро-вание привело к увеличению числа команд в наборе и числа микрокоманд в команде. Следствием этого явилось усложнение интегральных схем и сни-жение быстродействия выполнения программ. Один из возможных путей уст-ранения указанных недостатков состоит в использовании сокращенного набо-ра команд, организация которого подчинена увеличению скоростей их выпол-нения;

● RISC-архитектуру, которая относится к процессорам (компьютерам) с сокра-щенным набором команд (Reduced instruction Set Computer — RISC). Появле-ние RISC -архитектуры продиктовано тем, что многие CISC -команды и спо-собы адресации используются достаточно редко. Основная особенность RISC-архитектуры проявляется в том, что система команд состоит из неболь-шого количества часто используемых команд одинакового формата, которые могут быть выполнены за один командный цикл (такт) центрального процес-сора. Более сложные, редко используемые команды реализуются на про-граммном уровне. Однако за счет значительного повышения скорости испол-нения команд средняя производительность RISC-процессоров может оказать-ся выше, чем у процессоров с CISC-архитектурой.

{xtypo_quote}Большинство команд RISC -процессоров связано с операцией регистр-регистр. Для обращения к памяти оставлены наиболее простые с точки зре-ния временных затрат операции загрузки в регистры и записи в память. {/xtypo_quote}

Современные RISC -процессоры реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта, и используют небольшое число наи-более простых способов адресации (регистровую, индексную и некоторые другие).

Для сокращения количества обращений к внешней оперативной памяти RISC -процессоры содержат десятки-сотни регистров общего назначения (РОН), тогда как в CISC

-процессорах

всего 8-16 регистров. Обращение к внешней памяти в RISC-процессорах используется только в операциях за-грузки данных в РОН или пересылки результатов из РОН в память. За счет со-кращения аппаратных средств, необходимых для декодирования и выполне-ния сложных команд, достигается существенное упрощение интегральных схем RISC-процессоров и снижение их стоимости. Кроме того, значительно повышается производительность. Благодаря указанным достоинствам во многих современных

CI SC -процессорах (последние модели Pentium и К7) ис-пользуется RISC-ядро. При этом сложные CI SC-команды предварительно преобразуются в последовательность простых RISC-операций и быстро вы-полняются RISC-ядром;

● VLIW-архитектуру, которая относится к микропроцессорам с использованием очень длинных команд (Very Large Instruction Word— VLIW). Отдельные поля команды содержат коды, обеспечивающие выполнение различных операций. Одна VLIW -команда может выполнить сразу несколько операций одновремен-но в различных узлах микропроцессора. Формирование «длинных» VLIW - koманд производит соответствующий компилятор при трансляции программ, написанных на языке высокого уровня.

{xtypo_quote}VLIW -архитектура реализована в неко-торых типах современных микропроцессоров и является весьма перспектив-ной для создания нового поколения сверхвысокопроизводительных процес-соров. {/xtypo_quote}

По способу организации выборки команд и данных различа-ют два вида архитектур:

● принстонская архитектура, или архитектура фон-Неймана, особенностью которой является (рис. 2.1.1) использование:

Общей основной (оперативной) памяти для хранения программ и данных, что позволяет оперативно и эффективно перераспределять ее объем в за-висимости от решаемых задач в каждом конкретном случае применении микропроцессора;

Общей шины, по которой в процессор поступают команды и данные, а в опе-ративную память записываются результаты, что значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность. Чтобы отделить команду от данных, первым из памяти всегда поступает код выполняемой операции, а затем следуют данные. По умолчанию код операции загружается в регистр команд, а дан-ные — в блок регистров (рис. 2.1.1). Из-за ограниченного числа внешних выводов общая шина обычно работает в режиме временного мультиплек-сирования, т. е. противоположные направления обмена данными между микропроцессором, памятью или другими внешними устройствами разде-лены во времени.

Недостаток принстонской архитектуры

Использование общей шины для пе-редачи команд и данных ограничивает производительность цифровой системы;

● гарвардская архитектура (создатель Говард Айкен), особенностью которой является физическое разделение памяти команд (программ) и памяти данных (рис. 2.1.2). Это обстоятельство вызвано постоянно возрастающими требова-ниями к производительности микропроцессорных систем. Память команд и память данных соединяются с процессором отдельными шинами. Благодаря разделению потоков команд и данных, а также совмещению операций их вы-борки (и записи результатов обработки) обеспечивается более высокая про-изводительность, чем при использовании принстонской архитектуры.

Недостатки гарвардской архитектуры

Усложнение конструкции из-за ис-пользования отдельных шин для команд и данных; фиксированный объем па-мяти для команд и данных; увеличение общего объема памяти из-за невоз-можности ее оптимального перераспределения между командами и данными. Гарвардская архитектура получила широкое применение в микроконтрол-лерах — специализированных микропроцессорах для управления различными объектами, а также во внутренней структуре современных высокопроизводи-тельных микропроцессоров в кэш-памяти с раздельным хранением команд и данных.

В то же время во внешней структуре большинства микропроцессор-ных систем реализуются принципы принстонской архитектуры.

Отметим, что архитектура микропроцессора тесно связана с его структурой. Реализация тех или иных архитектурных особенностей требует введении в струк-туру микропроцессора соответствующих устройств и обеспечения механизмов их совместного функционирования.

1.6.1 Основные понятия

Развитие технологии обеспечивает возможность создания на кристалле все большего количества активных компонентов - транзисторов, которые могут быть использованы для реализации новых архитектурных и структурных решений, обеспечивающих повышение производительности и расширение функциональных возможностей микропроцессоров

Микропроцессорная техника включает технические и программные средства, используемые для построения различных микропроцессорных систем, устройств и персональных микроЭВМ.

Микропроцессор (МП) – программно-управляемое устройство, осуществляющее процесс цифровой обработки информации и управления им и построенное, как правило, на одной БИС.

Микропроцессорная система (МПС) представляет собой функционально законченное изделие, состоящее из одного или нескольких устройств, главным образом, микропроцессорных: микропроцессора и/или микроконтроллера.

Термин «микроконтроллер» (МК) вытеснил из употребления ранее использовавшийся термин «однокристальная микроЭВМ». Первый же патент на однокристальную микро-ЭВМ был выдан в 1971 году М. Кочрену и Г. Буну. Именно они предложили на одном кристалле разместить не только микропроцессор, но и память, устройства ввода-вывода. С появлением однокристальных микроЭВМ связывают начало эры компьютерной автоматизации в области управления. По-видимому, это обстоятельство и определило термин «микроконтроллер» (control - управление).

Однако впоследствии расширение сферы использования МК повлекло за собой развитие их архитектуры за счет размещения на кристалле устройств (модулей), отражающих своими функциональными возможностями специфику решаемых задач. Такие дополнительные устройства стали называться периферийными. Поэтому неслучайно в последнее время введен еще один термин - «интегрированный процессор» (ИП) , который определяет новый класс функционально-емких однокристальных устройств с другим составом модулей. По количеству и составу периферийных устройств ИП уступают МК и занимают промежуточное положение между МП и МК. По этой же причине появились не только семейства МК, которые объединяют родственные МК (с одинаковой системой команд, разрядностью), но и стали выделяться подвиды МК: коммуникационные, для управления и т. д.

Микроконтроллер (МК) – однокристальная ЭВМ или управляющий микропроцессор.

МП в настоящее время преимущественно используются для производства персональных ЭВМ, а МК и ИП являются основой создания различных встраиваемых систем, телекоммуникационного и портативного оборудования и т. д.

Архитектурой процессора называется комплекс его аппаратных и программныхсредств, предоставляемых пользователю. В это общее понятие входит набор программно-доступных регистров и исполнительных (операционных) устройств, система основных команд и способов адресации, объем и структура адресуемой памяти и т.д.

Архитектура тесно связана соструктурой , которая предусматривает наличие компонентов для реализации функций процессора.

1.6.2 Варианты архитектур микропроцессоров

В зависимости от набора выполняемых команд и способов адресации

CISC ( Complex Instruction Set Computer ) – архитектура реализована во многих типах микропроцессоров, выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации.

Например, микропроцессоры семейства Pentium. Они выполняют более 200 команд разной степени сложности, которые имеют размер от 1 до 15 байт и обеспечивают более 10 различных способов адресации).

Большое многообразие выполняемых команд и способов адресации позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач. Однако при этом существенноусложняется структура микропроцессора, особенно его устройства управления, что приводит к увеличению размеров и стоимости кристалла, снижению производительности. В то же время многие команды и способы адресации используются достаточно редко. Поэтому, начиная с 1980-х годов, интенсивное развитие получила архитектура процессоров с сокращенным набором команд ( RISC -процессоры).

RISC ( Reduced Instruction Set Computer ) – архитектура отличается использованием ограниченного набора команд фиксированного формата и сокращенного числа способов адресации. В результате существенно упрощается структура микропроцессора, сокращаются его размеры и стоимость, значительно повышается производительность.

Современные RISC-процессоры обычно реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта. Также значительно сокращается число используемых способов адресации. Обычно в RISC-процессорах все команды обработки данных выполняются только с регистровой или непосредственной адресацией. При этом для сокращения количества обращений к памяти RISC-процессоры имеют увеличенный объем внутреннего регистрового запоминающего устройства – от 32 до нескольких сотен регистров, тогда как в CISC-процессорах число регистров общего назначения обычно составляет 8-16.Обращение к памяти в RISC-процессорах используется только в операциях загрузки данных в РЭУ или пересылки результатов из РЭУ в память. При этом используется небольшое число наиболее простых способов адресации: косвенно-регистровая, индексная и некоторые другие.

Достоинства RISC-архитектуры привели к тому, что во многих современных CISC-процессорах используется RISC-ядро, выполняющее обработку данных. При этом поступающие сложные и разноформатные команды предварительно преобразуются в последовательность простых RISC-операций, быстро выполняемых этим процессорным ядром.

Таким образом работают, например, последние модели микропроцессоров Pentium и К7, которые по внешним показателям относятся к CISC-процессорам. Использование RISC-архитектуры является характерной чертой многих современных микропроцессоров.

VLIW ( Very Large Instruction Word ) – особенностью архитектуры является использование очень длинных команд(до 128 бит и более), отдельные поля которых содержат коды, обеспечивающие выполнение различных операций. Таким образом, одна команда вызывает выполнение сразу нескольких операций параллельно в различных операционных устройствах, входящих в структуру микропроцессора.

Архитектура появилась относительно недавно - в 1990-х годах.

В зависимостиот используемого варианта реализации памяти и организации выборки команд и данных в современных микропроцессорах реализуются следующие варианты архитектур:

Принстонская архитектура , которая часто называется архитектурой Фон-Неймана, характеризуется использованием общей оперативной памяти для хранения программ и данных. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные.

Достоинства архитектуры:

а) Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд, данных в зависимости от решаемых задач. Этим обеспечивается возможность эффективного использования имеющегося объема оперативной памяти в каждом конкретном случае применения микропроцессора;

б) использование общей шины для передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность.

Основным недостатком архитектуры является необходимость последовательной выборки команд и обрабатываемых данных по общей системной шине. При этом общая шина становится «узким местом» (bottleneck - «бутылочное горло»), которое ограничивает производительность цифровой системы.

Гарвардская архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды.

Достоинством архитектуры является более высокая производительность, чем при использовании Принстонской архитектуры, благодаря разделению потоков команд и данных и совмещению операций их выборки.

Недостатки архитектуры связаны с необходимостью проведения большего числа шин, а также с фиксированным объемом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи.

Поэтому приходится использовать память большего объема, коэффициент использования которой при решении разнообразных задач оказывается более низким, чем в системах с Принстонской архитектурой. Однако развитие микроэлектронной технологии позволило в значительной степени преодолеть указанные недостатки.

Гар вардская архитектура широко применяется во внутренней структуре современных высокопроизводительных микропроцессоров, где используется отдельная кэш-память для хранения команд и данных. В то же время во внешней структуре большинства микропроцессорных систем реализуются принципыПринстонской архитектуры .

Типовая структура микропроцессорной системы

Большинство микропроцессорных систем имеет магистрально-модульную структуру, в которой отдельные устройства (модули), входящие в состав системы, обмениваются информацией по общей системной шине–магистрали (рисунок 1.7).

Основным модулем системы является микропроцессор, в состав которого входят

устрой ство управления (УУ) ,

операционное устройство ,

регистровое запоминающее уст ройство (РЗУ) –внутренняя память, реализованная в виде набора регистров.

Опера тивное запоминающее устройство (ОЗУ) служит для хранения выполняемой программы (или ее фрагментов) и данных, подлежащих обработке. В простейших микропроцессорных системах объем ОЗУ составляет десятки и сотни байт, а современных персональных компьютерах, серверах и рабочих станциях он достигает сотен Мбайт и более. Так как обращение к ОЗУ по системной шине требует значительных затрат времени,в большинстве современных высокопроизводительных микропроцессоров дополнительно вводитсябыстродействующая промежуточная память (кэш-память) ограниченного объема (от нескольких Кбайт до сотен Кбайт).

Постоянное запоминающее устройство (ПЗУ) служит для хранения констант и стандартных (неизменяемых) программ. В ПЗУ обычно записываются программы начальной инициализации (загрузки) систем, тестовые и диагностические программы и другое служебное программное обеспечение, которое не меняется в процессе эксплуатации систем. В микропроцессорных системах, управляющих определенными объектами с использованием фиксированных или редко изменяемых программ, для их хранения также обычно используется ПЗУ (память ROM – Read-Only Memory) или репрограммируемое ПЗУ (память EEPROM – Electrically Erased Programmable Read-Only Memory или флэш-память).

Интер фейсные устройства (ИУ) служат для подключения к шине остальных устройств, которые являются внешними по отношению к системе. ИУ реализуют определенные протоколы параллельного или последовательного обмена. Внешними устройствами могут быть клавиатура, монитор, внешние запоминающие устройства (ВЗУ), использующие гибкие или жесткие магнитные диски, оптические диски (CD-ROM), магнитные ленты и другие виды носителей информации, датчики и преобразователи информации (аналого-цифровые или цифроаналоговые), разнообразные исполнительные устройства (индикаторы, принтеры, электродвигатели, реле и другие).

Для реализации различных режимов работы к системе могут подключаться дополнительные устройства – контроллеры прерываний, прямого доступа к памяти и другие, реализующие необходимые специальные функции управления.

Данная структура соответствует архитектуре Фон-Неймана, предложенной этим ученым в 1940-х годах для реализации первых моделей цифровых ЭВМ.

УУ – устройство управления

ОУ – операционное устройство

РЗУ– регистровое запоминающее устройство

ОЗУ – оперативное запоминающее устройство

ПЗУ – постоянное запоминающее устройство

ИУ – интерфейсное устройство

Рисунок 1.7 – Типовая структура микропроцессорной системы

Системная шина содержит несколько десятков (в сложных системах более 100) проводников, которые в соответствии с их функциональным назначением подразделяются на отдельные шины:

шина адреса А , служит для передачи адреса, который формируется микропроцессором и позволяет выбрать необходимую ячейку памяти ОЗУ (ПЗУ) или требуемое ИУ при обращении к внешнему устройству;

шина данных D , служит для выборки команд, поступающих из ОЗУ или ПЗУ в УУ микропроцессора, и для пересылки обрабатываемых данных (операндов) между микропроцессором и ОЗУ или ИУ (внешним устройством);

шина управления С , служит для передачи разнообразных управляющих сигналов, определяющих режимы работы памяти (запись или считывание), интерфейсных устройств (ввод или вывод информации) и микропроцессора (запуск, запросы внешних устройств на обслуживание, информация о текущем режиме работы) и другие сигналы.

Архитектура микропроцессора

Понятие микропроцессора

Появление технологии интегральных микросхем - новый этап в развитии вычислительной техники. В результате разработки процессоров на основе микросхем - размеры и форма цифровых ЭВМ значительно уменьшились.

Микропроцессор (МП) - это программно управляемое устройство, которое предназначено для обработки цифровой информации и управления процессом этой обработки и выполнено в виде одной или нескольких больших интегральных схем (БИС) .

Понятие большая интегральная схема в настоящее время четко не определено. Ранее считалось, что к этому классу следует относить микросхемы, содержащие более 1000 элементов на кристалле. И действительно, в эти параметры укладывались первые микропроцессоры. Например, 4-разрядная процессорная секция микропроцессорного комплекта К584, выпускавшегося в конце 1970-х годов, содержала около 1500 элементов. Сейчас, когда микропроцессоры содержат десятки миллионов транзисторов и их количество непрерывно увеличивается, под БИС будем понимать функционально сложную интегральную схему.

Степень интеграции схем (в ГОСТе):

Интегральная схема с низкой степенью интеграции <10 транзисторов;

Схема со средней степенью интеграции < 100 транзисторов;

Большая интегральная схема (БИС) > 100 транзисторов (~ 1000 транзисторов)

Микропроцессорная система (МПС) представляет собой функционально законченное изделие, состоящее из одного или нескольких устройств, основу которой составляет микропроцессор.

Микропроцессор характеризуется большим количеством параметров и свойств, так как он является, с одной стороны, функционально сложным вычислительным устройством, а с другой - электронным прибором, изделием электронной промышленности .

Типы архитектур микропроцессоров

Как средство вычислительной техники микропроцессор характеризуется прежде всего своей архитектурой, то есть совокупностью программно-аппаратных свойств, предоставляемых пользователю. Сюда относятся система команд, типы и форматы обрабатываемых данных, режимы адресации, количество и распределение регистров, принципы взаимодействия с оперативной памятью и внешними устройствами (характеристики системы прерываний, прямой доступ к памяти и т. д.).

По своей архитектуре микропроцессоры разделяются на несколько типов (рис. 3).

Рис. 3. Классификация микропроцессоров

Универсальные микропроцессоры

Универсальные микропроцессоры предназначены для решения задач цифровой обработки различного типа информации от инженерных расчетов до работы с базами данных, не связанных жесткими ограничениями на время выполнения задания. Этот класс микропроцессоров наиболее широко известен. К нему относятся такие известные микропроцессоры, как МП ряда Pentium фирмы Intel и МП семейства Athlon фирмы AMD.

Характеристики универсальных микропроцессоров:

Разрядность: определяется максимальной разрядностью целочисленных данных, обрабатываемых за 1 такт, то есть фактически разрядностью арифметико-логического устройства (АЛУ);

Виды и форматы обрабатываемых данных;

Система команд, режимы адресации операндов;

Емкость прямоадресуемой оперативной памяти: определяется разрядностью шины адреса;

Частота внешней синхронизации. Для частоты синхронизации обычно указывается ее максимально возможное значение, при котором гарантируется работоспособность схемы. Для функционально сложных схем, к которым относятся и микропроцессоры, иногда указывают также минимально возможную частоту синхронизации. Уменьшение частоты ниже этого предела может привести к отказу схемы. В то же время в тех применениях МП, где не требуется высокое быстродействие, снижение частоты синхронизации - одно из направлений энергосбережения. В ряде современных микропроцессоров при уменьшении частоты он переходит в «спящий режим», при котором сохраняет свое состояние. Частота синхронизации в рамках одной архитектуры позволяет сравнить производительность микропроцессоров. Но разные архитектурные решения влияют на производительность гораздо больше, чем частота;

Производительность: определяется с помощью специальных тестов, при этом совокупность тестов подбирается таким образом, чтобы они по возможности покрывали различные характеристики микроархитектуры процессоров, влияющие на производительность.

Универсальные микропроцессоры принято разделять на CISC- и RISC-микропроцессоры. CISC-микропроцессоры (completed instruction set computing - вычисления с полной системой команд) имеют в своем составе весь классический набор команд с широко развитыми режимами адресации операндов. Именно к этому классу относятся, например, микропроцессоры типа Pentium. В то же время RISC-микропроцессоры (reduced instruction set computing - вычисления с сокращенной системой команд) используют, как следует из определения, уменьшенное количество команд и режимов адресации. Здесь, прежде всего, следует выделить такие микропроцессоры, как Alpha 21x64, Power PC. Количество команд в системе команд - наиболее очевидное, но на сегодняшний день не самое главное различие в этих направлениях развития универсальных микропроцессоров. Другие различия мы будем рассматривать по мере изучения особенностей их архитектуры.

МикропроцессорыВведениеЭВМ получили широкое распространение, начиная с 50-х годов. Прежде это были очень большие и дорогие устройства, используемые лишь в государственных учреждениях и крупных фирмах. Размеры и форма цифровых ЭВМ неузнаваемо изменились в результате разработки новых устройств, называемых микропроцессорами. Микропроцессор (МП) - это программно-управляемое электронное цифровое устройство, предназначенное для обработки цифровой информации и управления процессом этой обработки, выполненное на одной или нескольких интегральных схемах с высокой степенью интеграции электронных элементов. В 1970 году Маршиан Эдвард Хофф из фирмы Intel сконструировал интегральную схему, аналогичную по своим функциям центральному процессору большой ЭВМ - первый микропроцессор Intel-4004, который уже в 1971 году был выпущен в продажу. Это был настоящий прорыв, ибо МП Intel-4004 размером менее 3 см был производительнее гигантской машины ENIAC. Правда работал он гораздо медленнее и мог обрабатывать одновременно только 4 бита информации (процессоры больших ЭВМ обрабатывали 16 или 32 бита одновременно), но и стоил первый МП в десятки тысяч раз дешевле. Кристалл представлял собой 4-разрядный процессор с классической архитектурой ЭВМ гарвардского типа и изготавливался по передовой p-канальной МОП технологии с проектными нормами 10 мкм. Электрическая схема прибора насчитывала 2300 транзисторов. МП работал на тактовой частоте 750 кГц при длительности цикла команд 10,8 мкс. Чип i4004 имел адресный стек (счетчик команд и три регистра стека типа LIFO), блок РОНов (регистры сверхоперативной памяти или регистровый файл - РФ), 4-разрядное параллельное АЛУ, аккумулятор, регистр команд с дешифратором команд и схемой управления, а также схему связи с внешними устройствами. Все эти функциональные узлы объединялись между собой 4-разрядной ШД. Память команд достигала 4 Кбайт (для сравнения: объем ЗУ миниЭВМ в начале 70-х годов редко превышал 16 Кбайт), а РФ ЦП насчитывал 16 4-разрядных регистров, которые можно было использовать и как 8 8-разрядных. Такая организация РОНов сохранена и в последующих МП фирмы Intel . Три регистра стека обеспечивали три уровня вложения подпрограмм. МП i4004 монтировался в пластмассовый или металлокерамический корпус типа DIP (Dual In-line Package ) всего с 16 выводами. В систему его команд входило всего 46 инструкций. Вместе с тем кристалл располагал весьма ограниченными средствами ввода/вывода, а в системе команд отсутствовали операции логической обработки данных (И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ), в связи с чем их приходилось реализовывать с помощью специальных подпрограмм. Модуль i4004 не имел возможности останова (команды HALT) и обработки прерываний. Цикл команды процессора состоял из 8 тактов задающего генератора. Была мультиплексированная ША (шина адреса)/ШД (шина данных), адрес 12-разрядный передавался по 4-разряда. 1 апреля 1972 г. фирма Intel начала поставки первого в отрасли 8-разрядного прибора i8008. Кристалл изготавливался по р-канальной МОП-технологии с проектными нормами 10 мкм и содержал 3500 транзисторов. Процессор работал на частоте 500 кГц при длительности машинного цикла 20 мкс (10 периодов задающего генератора). В отличие от своих предшественников МП имел архитектуру ЭВМ принстонского типа, а в качестве памяти допускал применение комбинации ПЗУ и ОЗУ. По сравнению с i4004 число РОН уменьшилось с 16 до 8, причем два регистра использовались для хранения адреса при косвенной адресации памяти (ограничение технологии - блок РОН аналогично кристаллам 4004 и 4040 в МП 8008 был реализован в виде динамической памяти). Почти вдвое сократилась длительность машинного цикла (с 8 до 5 состояний). Для синхронизации работы с медленными устройствами был введен сигнал готовности READY. Система команд насчитывала 65 инструкций. МП мог адресовать память объемом 16 Кбайт. Его производительность по сравнению с четырехразрядными МП возрасла в 2,3 раза. В среднем для сопряжения процессора с памятью и устройствами ввода/вывода требовалось около 20 схем средней степени интеграции. Возможности р-канальной технологии для создания сложных высокопроизводительных МП были почти исчерпаны, поэтому "направление главного удара" перенесли на n-канальную МОП технологию. 1 апреля 1974 МП Intel 8080 был представлен вниманию всех заинтересованных лиц. Благодаря использованию технологии п-МОП с проектными нормами 6 мкм, на кристалле удалось разместить 6 тыс. транзисторов. Тактовая частота процессора была доведена до 2 Мгц , а длительность цикла команд составила уже 2 мкс. Объем памяти, адресуемой процессором, был увеличен до 64 Кбайт. За счет использования 40-выводного корпуса удалось разделить ША и ШД, общее число микросхем, требовавшихся для построения системы в минимальной конфигурации сократилось до 6 (рис. 1). Рис. 1. Микропроцессор Intel 8080. В РФ были введены указатель стека, активно используемый при обработке прерываний, а также два программнонедоступных регистра для внутренних пересылок. Блок РОНов был реализован на микросхемах статической памяти. Исключение аккумулятора из РФ и введение его в состав АЛУ упростило схему управления внутренней шиной. Новое в архитектуре МП - использование многоуровневой системы прерываний по вектору. Такое техническое решение позволило довести общее число источников прерываний до 256 (до появления БИС контроллеров прерываний схема формирования векторов прерываний требовала применения до 10 дополнительных чипов средней интеграции). В i8080 появился механизм прямого доступа в память (ПДП) (как ранее в универсальных ЭВМ IBM System 360 и др.). ПДП открыл зеленую улицу для применения в микроЭВМ таких сложных устройств, как накопители на магнитных дисках и лентах дисплеи на ЭЛТ, которые и превратили микроЭВМ в полноценную вычислительную систему. Традицией компании, начиная с первого кристалла, стал выпуск не отдельного чипа ЦП, а семейства БИС, рассчитанных на совместное использование. |

Архитектура микропроцессора

Основные характеристики микропроцессора

Микропроцессор характеризуется:

1) тактовой частотой, определяющей максимальное время выполнения переключения

элементов в ЭВМ;

2) разрядностью, т.е. максимальным числом одновременно обрабатываемых двоичных

разрядов.

Разрядностть

МП обозначается m

/n

/k

/ и включает:

m

- разрядность внутренних регистров, определяет

принадлежность к тому или иному классу процессоров;

n

- разрядность шины данных, определяет скорость

передачи информации;

k

- разрядность шины адреса, определяет размер

адресного пространства. Например, МП i8088 характеризуется значениями m

/n

/k=16/8/20;

3) архитектурой. Понятие архитектуры микропроцессора включает в себя систему

команд и способы адресации, возможность совмещения выполнения команд во

времени, наличие дополнительных устройств в составе микропроцессора, принципы и

режимы его работы. Выделяют понятия микроархитектуры

и макроархитектуры

.

Микроархитектура микропроцессора - это аппаратная организация и логическая структура микропроцессора, регистры, управляющие схемы, арифметико-логические устройства, запоминающие устройства и связывающие их информационные магистрали.

Макроархитектура - это система команд, типы обрабатываемых данных, режимы адресации и принципы работы микропроцессора.

В общем случае под архитектурой ЭВМ понимается абстрактное представление машины в терминах основных функциональных модулей, языка ЭВМ, структуры данных.

Структура типового микропроцессора

Архитектура типичной небольшой вычислительной системы на основе микроЭВМ показана на рис. 2.1 Т акая микроЭВМ содержит все 5 основных блоков цифровой машины: устройство ввода информации, управляющее устройство (УУ), арифметико-логическое устройство (АЛУ) (входящие в состав микропроцессора), запоминающие устройства (ЗУ) и устройство вывода информации.

Рис. 2.1. Архитектура типового микропроцессора.

Микропроцессор координирует работу всех устройств цифровой системы с помощью шины управления (ШУ). Помимо ШУ имеется 16-разрядная адресная шина (ША), которая служит для выбора определенной ячейки памяти, порта ввода или порта вывода. По 8-разрядной информационной шине или шине данных (ШД) осуществляется двунаправленная пересылка данных к микропроцессору и от микропроцессора. Важно отметить, что МП может посылать информацию в память микроЭВМ или к одному из портов вывода, а также получать информацию из памяти или от одного из портов ввода.

Постоянное запоминающее устройство (ПЗУ) в микроЭВМ содержит некоторую программу (на практике программу инициализации ЭВМ). Программы могут быть загружены в запоминающее устройство с произвольной выборкой (ЗУПВ) и из внешнего запоминающего устройства (ВЗУ). Это программы пользователя.

В качестве примера, иллюстрирующего работу микроЭВМ

,

рассмотрим процедуру, для реализации которой нужно выполнить следующую

последовательность элементарных операций:

1. Нажать клавишу с буквой "А" на клавиатуре.

2. Поместить букву "А" в память микроЭВМ

.

3. Вывести букву "А" на экран дисплея.

Это типичная процедура ввода-запоминания-вывода, рассмотрение которой дает возможность пояснить принципы использования некоторых устройств, входящих в микроЭВМ .

На рис. 2.2 приведена подробная диаграмма выполнения

процедуры ввода-запоминания-вывода. Обратите внимание, что команды уже

загружены в первые

шесть ячеек памяти. Хранимая

программа содержит следующую цепочку команд:

1. Ввести данные из порта ввода 1.

2. Запомнить данные в ячейке памяти 200.

3. Переслать данные в порт вывода 10.

Рис. 2.2. Диаграмма выполнения процедуры ввода-запоминания-вывода.

В данной программе всего три команды, хотя на рис. 2.2 может показаться, что в памяти программ записано шесть команд. Это связано с тем, что команда обычно разбивается на части. Первая часть команды 1 в приведенной выше программе - команда ввода данных. Во второй части команды 1 указывается, откуда нужно ввести данные (из порта 1). Первая часть команды, предписывающая конкретное действие, называется кодом операции (КОП), а вторая часть - операндом. Код операции и операнд размещаются в отдельных ячейках памяти программ. На рис. 2.2 КОП хранится в ячейке 100, а код операнда - в ячейке 101 (порт 1); последний указывает откуда нужно взять информацию.

В МП на рис. 2.2 выделены еще два новых блока - регистры: аккумулятор и регистр команд.

Рассмотрим прохождение команд и данных внутри микроЭВМ с помощью занумерованных кружков на диаграмме. Напомним, что микропроцессор - это центральный узел, управляющий перемещением всех данных и выполнением операций.

Итак, при выполнении типичной процедуры ввода-запоминания-вывода в микроЭВМ

происходит следующая последовательность действий:

1. МП выдает адрес 100 на шину адреса. По шине управления поступает сигнал,

устанавливающий память программ (конкретную микросхему) в режим считывания.

2. ЗУ программ пересылает первую команду ("Ввести данные") по шине

данных, и МП получает это закодированное сообщение. Команда помещается в

регистр команд. МП декодирует (интерпретирует) полученную команду и определяет,

что для команды нужен операнд.

3. МП выдает адрес 101 на

ША; ШУ используется для

перевода памяти программ в режим считывания.

4. Из памяти программ на ШД пересылается операнд "Из порта 1". Этот

операнд находится в программной памяти в ячейке 101. Код операнда (содержащий

адрес порта 1) передается по ШД к МП и направляется в регистр команд. МП теперь

декодирует полную команду ("Ввести данные из порта 1").

5. МП, используя ША и ШУ, связывающие

его с

устройством ввода, открывает порт 1. Цифровой код буквы "А"

передается в аккумулятор внутри МП и запоминается.В

ажно

отметить, что при обработке каждой программной

команды МП действует согласно микропроцедуре

выборки-декодирования-исполнения.

6. МП обращается к ячейке 102 по

ША. ШУ используется

для перевода памяти программ в режим считывания.

7. Код команды "Запомнить данные" подается на ШД и пересылается в МП,

где помещается в регистр команд.

8. МП дешифрирует эту команду и определяет, что для нее нужен операнд. МП

обращается к ячейке памяти 103 и приводит в активное состояние вход считывания

микросхем памяти программ.

9. Из памяти программ на ШД пересылается код сообщения "В ячейке памяти

200". МП воспринимает этот операнд и помещает его в регистр команд. Полная

команда "Запомнить данные в ячейке памяти 200" выбрана из памяти

программ и декодирована.

10. Теперь начинается процесс выполнения команды. МП пересылает адрес 200 на ША

и активизирует вход записи, относящийся к памяти данных.

11. МП направляет хранящуюся в аккумуляторе информацию в память данных. Код

буквы "А" передается по ШД и записывается в ячейку 200 этой памяти.

Выполнена вторая команда. Процесс запоминания не разрушает содержимого

аккумулятора. В нем по-прежнему находится код буквы "А".

12. МП обращается к ячейке памяти 104 для выбора очередной команды и переводит

память программ в режим считывания.

13. Код команды вывода данных пересылается по ШД к МП, который помещает ее в

регистр команд, дешифрирует и определяет, что нужен операнд.

14. МП выдает адрес 105 на ША и устанавливает память программ в режим

считывания.

15. Из памяти программ по ШД к МП поступает код операнда "В порт 10",

который далее помещается в регистр команд.

16. МП дешифрирует полную команду "Вывести данные в порт 10". С помощью ША и ШУ, связывающих его с устройством вывода, МП

открывает порт 10, пересылает код буквы "А" (все еще находящийся в аккумуляторе)

по ШД.

Буква "А" выводится через порт 10 на экран дисплея.

В большинстве микропроцессорных систем (МПС) передача информации осуществляется способом, аналогичным рассмотренному выше. Наиболее существенные различия возможны в блоках ввода и вывода информации.

Подчеркнем еще раз, что именно микропроцессор является ядром системы и осуществляет управление всеми операциями. Его работа представляет последовательную реализацию микропроцедур выборки-дешифрации-исполнения. Однако фактическая последовательность операций в МПС определяется командами, записанными в памяти программ.

Таким образом, в МПС микропроцессор выполняет следующие

функции:

- выборку команд программы из основной памяти;

- дешифрацию команд;

- выполнение арифметических, логических и других операций, закодированных в

командах;

- управление пересылкой информации между регистрами и основной памятью, между

устройствами ввода/вывода;

- отработку сигналов от устройств ввода/вывода, в том числе реализацию

прерываний с этих устройств;

- управление и координацию работы основных узлов МП.