Процессорные модули и базовые платы. Процессорный модуль СМ-Х255 компании CompuLab

Отправить свою хорошую работу в базу знаний просто. Используйте форму, расположенную ниже

Студенты, аспиранты, молодые ученые, использующие базу знаний в своей учебе и работе, будут вам очень благодарны.

Размещено на http://www.allbest.ru/

Введение

Процессорный модуль представляет собой функционально законченное устройство со встроенной функцией отладки целевого программного обеспечения. Он содержит разъемы, на которые выведены все контакты микропроцессора. Процессорный модуль обеспечивает корректный старт и инициализацию микропроцессора после аппаратного сброса. Он может функционировать под управлением инструментального компьютера или без него. Взаимодействие инструментального компьютера и процессорного модуля осуществляется посредством отладочного интерфейса.

Модуль не содержит ничего необычного для микропроцессорной системы и использует только те свойства микропроцессора, которые являются общими для большинства из них. Благодаря этому достигается независимость структуры модуля от выбора микропроцессора. Разработчику предлагается строить целевую микропроцессорную систему на основе процессорного модуля со встроенными функциями отладки и начальной загрузки.

Метод проектирования микропроцессорной системы с использованием отладочного процессорного модуля позволяет ускорить и удешевить процесс разработки целевой системы. Использование метода позволяет обойтись без затрат связанных с приобретением внутрисхемного эмулятора, эмулятора ПЗУ и программной модели микропроцессора, упростить технологию разработки и отладки частей целевой системы связанных непосредственно с микропроцессором. Пользователь приобретает сразу часть целевой системы со встроенными функциями отладки и диагностики.

В процессе выполнения данного курсового проекта будет осуществлено проектирование процессорного модуля - независимого устройства, которое может выполнять два заданных действия над операндами. Результатом проекта будет схема устройства, отвечающего требованиям к системам обработки информации.

1 . Анализ задания

Электронная система, реализующая сложный алгоритм обработки данных, может быть условно разделена на две функционально связанные подсистемы - управляющий и операционный автомат. Взаимодействие двух этих подсистем приведено на рис. 1.1.

Управляющий автомат определяет порядок реализации вычислительных операций и отображает граф-схему функционирования электронной системы. Входной информацией для управляющего автомата является множество осведомительных сигналов {X} и множество внешних флагов ветвления {F}, результатом функционирования - множество признаков выполняемых микроопераций {Y}.

Операционный автомат осуществляют вычислительные действия над операндами. Структурно операционный автомат состоит из элементов памяти (регистров), осуществляющих хранение значений операндов, и комбинационных схем, отвечающих за выполнение микроопераций. Входной информацией для операционного автомата являются линии данных {D} и множество выполняемых в данном такте микроопераций {Y}, выходами являются линии результата {R} и выработанные признаки результата {X}, используемые в управляющем автомате.

Согласно полученного задания необходимо реализовать процессорный модуль, выполняющий алгоритмы следующих действий: умножение целых двоичных беззнаковых чисел, начиная с младших разрядов множителя, преобразование двоично-десятичного числа в двоичное.

На рисунках 1.2 и 1.3 приведены ГСА действий, которые должен выполнять проектируемый процессорный модуль.

Рисунок 1.2 - Умножение целых двоичных беззнаковых чисел, начиная с младших разрядов множителя

Рисунок 1.3 - Умножение целых двоичных беззнаковых чисел, начиная со старших разрядов множителя

Для выполнения поставленной задачи необходимо объединить две ГСА, т. к. проектируемый процессорный модуль должен выполнять две операции. Для выбора одной из операций в объединенную ГСА, которая изображена на рисунке 1.4 добавлена условная вершина, проверяющего состояние регистра COP (code of operation). Данные в СОР являются, как и операнды, входной информацией для проектируемого процессорного модуля.

В объединенной ГСА относительно исходных алгоритмов была изменена операция обнуления регистра С. Обнуление младших восьми разрядов регистра было изменено на обнуление всех разрядов, т. к. это при проектировании управляющего автомата позволит сократить количество признаков выполняемых микроопераций {Y}. С той же целью была создана общая для обеих ГСА вершина вывода результата.

Таким образом, при проектировании процессорного модуля необходимо использовать объединенную ГСА, описывающую алгоритмы выполнения предусмотренных действий. Процессорный модуль будет логически разбит на две подсистемы - ОА и УА, которые будут проектироваться как независимые устройства.

Рисунок 1.4 - Общая ГСА

2 . Проектирование операционного автомата

2.1 Общие вопросы функционирования операционных атоматов

Функции ОА сводятся к вводу-выводу и хранению слов информации, выполнению микроопераций и вычислению логических условий. Чтобы реализовать эти действия, необходим набор элементов, достаточный для построения структур с заданными функциями. Такой набор элементов называется структурным базисом ОА.

Основными операционными элементами, используемыми в ОА, являются:

Управляемые шины, обеспечивающие передачу информации;

Регистры;

Комбинационные схемы, используемые для выполнения преобразований и формирования логических условий.

В общем виде структура ОА представлена на рисунке 2.1, где Ф - комбинационные схемы, выполняющие преобразование, S - память, ? - комбинационные схемы, формирующие осведомительные сигналы.

Рисунок 2.1 - Общая структура ОА

процессорный модуль обработка информация

2.2 Структурная организация М-автоматов

Согласно заданию, ОА для проектируемого процессорного модуля должен быть типа М. М-автоматом называется такой ОА, который синтезируется на основе принципа обобщения комбинационных схем, используемых для выполнения всех микроопераций. М-автомат имеет наименьшие аппаратные затраты, однако недостатком М-автомата является то, что он не может выполнять больше одной микрооперации преобразования за один такт работы. Следовательно, производительность М-автомата невысока.

Принцип обобщения комбинационных схем обуславливает структуру автомата, представленную на рисунке 2.2.

Рисунок 2.2 - Обобщенная структура ОА типа М

В такой структуре микрооперации, связанной с преобразованием y p: S k:

M (S i , S j), ставится в соответствие следующий набор операторов:

M: z:= ? m (A 1 , A 2);

y p = {a i , b i , ? m , d k }.

2.3 Проектирование М-автомата

Разработка структуры М-автомата подразумевает выполнение следующих этапов:

1. Для автомата выберем регистры, которые будут хранить результаты микроопераций:

A (7:0), B (7: 0), C (15: 0), CnT (3:0), COP.

2. Распределим регистры по двум шинам А 1 и А 2:

Arg1 = {C}, Arg1 (15: 0);

Arg2 = {A, B}, Arg2 (7: 0).

3. Определим микрооперации, выполняемые М-автоматом:

Таблица 2.1 - Операции для М-автомата

|

Микрооперация |

Результат |

|||||

|

C (15:0):=C (15:0)+A (7:0) |

Z=Arg1 (15:0)+Arg2 (7:0) |

|||||

|

B (7:0):=R1 (C(0).B (7:1)) |

Z=R1 (Arg1 (0).Arg2 (7:1)) |

|||||

|

C (7:0):=R1 (CF.C (7:1)) |

Z=R1 (CF. Arg1 (7:1)) |

|||||

|

R (15:0):=C (7:0).B (7:0) |

||||||

|

C (15:0):=L1 (C(14:0).0) |

Z=L1 (Arg1 (14:0).0) |

|||||

|

B (7:0):=L1 (B(6:0).0) |

Z=L1 (Arg2 (6:0).0) |

|||||

|

R (15:0):=C (15:0) |

4. Выделим классы эквивалентных микроопераций и найдем для них обобщенные микрооператоры:

5. Построим схему М-автомата уровня регистровых передач:

Рисунок 2.3 - Схема М-автомата уровня регистровых передач

3 . Проектирование управляющего автомата

3.1 Общие вопросы функционирования устройств управления с жёсткой логикой

Под УУ понимается совокупность блоков и узлов процессора, обеспечивающих координированные работы всех устройств ЭВМ и управление ими для всех принятых режимов.

УУ, реализуя программы, организовывают все необходимые действия по приёму, оценке и преобразованию исходной информации с целью получения и выдачи необходимых результатов. Т. о. УУ может считаться преобразованием первично-командной информации, представленной командами системы, во вторично-командную информацию, представленную формируемыми УУ, исполнительными адресами, кодами и управляющего сигнала, воздействие которых на соответствующие узлы и блоки приводит к выполнению заданных операций.

Последовательность выполнения программы:

выбор команды из ОП

декодирование операций

определение исполнительных адресов операндов

выборка операндов в кэш

выполнение операций

Рисунок 3.1 - Общая структура УУ

БУК осуществляет хранение считанной из памяти команды и формирует адреса следующей команды. Считывание из памяти очередной команды, преобразование адресной и операционной частей команды осуществляет БУО.

Для выработки синхронизирующих сигналов и согласования работы БУК и БУО используется БМУ.

При использовании «жёсткой» логики УА строятся из разрозненных комбинационных схем и элементов памяти. Закон функционирования УА определяется порядком соединения элементов между собой.

Основными элементами, с помощью которых могут быть построены УА, являются:

1 Элементы задержки (D-триггер)

2 Распределители сигналов (сдвигающие регистры)

3 Как цифровой автомат

3.2 Уточненная граф-схема алгоритма

Для проектирования управляющего автомата необходимо использовать уточненную ГСА, которая учитывает тип операционного автомата.

Преобразование объединенной ГСА в уточненную включает следующие действия:

1. замена микроопераций их условными обозначениями y i ;

2. разделение операционных вершин с n микрооперациями преобразования на n операционных вершин, т. к. ОА типа М не может выполнять больше одной микрооперации преобразования за один такт работы;

3. разметка состояний управляющего автомата по правилам:

Состояние после «начала» и перед «концом» должно иметь метку

Состояние после каждой операторной вершины должно иметь метку

Рисунок 3.2 - Уточненная (размеченная) ГСА

3.3 Проектирование управляющего автомата с жёсткой логикой

Разработка структуры УА подразумевает выполнение следующих этапов:

По размеченной ГСА строится граф переходов алгоритма:

Рисунок 3.3 - Граф переходов управляющего автомата

Таблица 3.1 - Кодирование состояний

|

Состояние |

Количество входов |

Кодировка |

|

Таблица 3.2 - Структурная таблица переходов управляющего автомата

Исходное состояние

Двоичный код исходного состояния

Результирующее состояние

Двоичный код результирующего состояния

Условие перехода

Формируемый выход

Функции возбуждения

Из данной таблицы можно получить следующие зависимости:

Для дешифратора состояний:

Для функций выхода

Для функции возбуждения триггеров

Построим схему УА уровня регистровых передач:

Согласно обобщенной структуре управляющего автомата для построения схемы используются следующие элементы:

Т-триггер

DC - декодирующее устройство, преобразующее позиционный двоичный код;

MX - мультиплексор, выбирающий одно из проверяемых логических условий;

Рисунок 3.4 - Схема УА уровня регистровых передач

4 . Проектирование процессорного модуля

Согласно декомпозиции процессорного модуля, представленной на рисунке 1.1, проектирование заключалось в выполнении двух этапов: проектирование операционного устройства и управляющего автомата.

Очевидно, что полученный процессорный модуль является соединением двух отдельных устройств - ОА и УА. На входы всего процессорного модуля подаются операнды (D 1 , D 2), условие выбора операции (СОР или D 3) и управляющие сигналы (Clk, Start, Stop, Reset). Внутреннее взаимодействие между ОА и УА заключается во взаимопередаче сигналов: ОА генерирует значения вычисленных логических условий {X} на каждом такте, УА формирует сигналы выполнения необходимых на данном такте микроопераций {Y}. Также операционное устройство формирует результат выполнения заданного значением регистра СОР действия, который подается на выходную шину R.

Помимо схем ОА и УА уровня регистровых передач результатом выполнения курсового проекта являются тексты VHDL-моделей управляющего устройства, операционного автомата и процессорного модуля. VHDL-модель процессорного модуля включает в себя в качестве компонентов модели ОА и УА.

5 . Анализ результатов синтеза

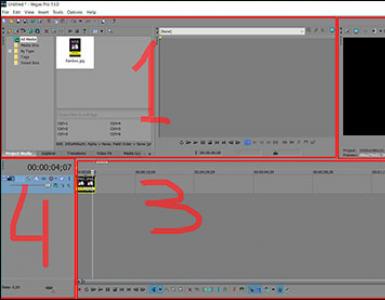

В результате автоматизированного синтеза были получены модели операционного автомата, управляющего устройства и всего процессорного модуля. Оценить работу разработанных компонентов можно с помощью полученных временных диаграмм, построенных в среде проектирования.

5.1 Тестирование VHDL -м одели операционного устройства

После разработки VHDL-модели ОА была получена временная диаграмма работы устройства, представленная на рисунке 5.1.

Рисунок 5.1 - Временная диаграмма работы VHDL-модели ОА

Моделирование работы ОА осуществлялось при подаче на входы устройства входных данных (d1, d2, d3), текущей микрокоманды и сигналов синхронизации (clk) и асинхронного сброса (rst). В результате моделирования и отладки был сделан вывод о соответствии работы устройства требованиям к ОА. (Текст VHDL-модели операционного автомата - в приложении 1).

5.2 Тестирование VHDL -м одели управляющего устройства

После разработки VHDL-модели УА была получена временная диаграмма работы устройства, представленная на рисунке 5.2.

Рисунок 5.2 - Временная диаграмма работы VHDL-модели УА

Для моделирования работы управляющего устройства на входы устройства были поданы сигналы синхронизации (clk) и асинхронного сброса (rst) а также значения вычисленных операционным автоматом логических условий. (Текст VHDL-модели управляющего автомата - в приложении 2).

Моделирование работы устройства осуществлялось по стратегии обхода всех дуг. В результате моделирования был сделан вывод о работоспособности модели, т. к. во всех состояниях УА в качестве выходного вектора подавались сигналы микроопераций, соответствующие отмеченным в уточненной ГСА.

5.3 Тестирование VHDL -м одели процессорного модуля

После разработки VHDL-модели УА были получены временные диаграммы выполнения двух действий, представленные на рисунках 5.3 и 5.4. Для моделирования на входы модели процессорного модуля были поданы данные для выполняемого действия (d1, d2 - операнды; d3 - код выполняемой операции). Результат выполнения операции был получен на выходной шине r.

Рисунок 5.3 - Умножение целых двоичных беззнаковых чисел, начиная с младших разрядов множителя

Проверка результатов моделирования работы, представленных на рисунке 5.3:

28 * 10 = 280, или

00011100 * 00001010 =100011000.

Рисунок 5.4 - Умножение целых двоичных беззнаковых чисел, начиная со старших разрядов множителя

При моделировании получен верный результат.

Выводы

Результатом выполнения курсового проекта является процессорный модуль, состоящий из операционного М-автомата и управляющего автомата с жёсткой логикой типа Мили, и выполняющий действия, согласно заданию: умножение целых двоичных беззнаковых чисел, начиная со старших разрядов множителя и умножение целых двоичных беззнаковых чисел, начиная с младших разрядов множителя

Исходными данными к проектированию были граф-схемы алгоритмов заданных действий, типы ОА и УА и разрядность операндов.

При выполнении курсового проекта были получены знания по организации и функционированию сложных цифровых систем обработки информации, получены практические навыки по проектированию процессорного модуля с использованием языка VHDL.

В результате анализа автоматизированного синтеза устройств можно сделать вывод о правильном и полном выполнении задания к курсовому проектированию, т. к. разработанный процессорный модуль правильно выполняет предусмотренные заданием действия.

Список использованных источников

1. Кораблев Н.М. - Конспект лекций по дисциплине «Компьютерная схемотехника» - Харьков, 2010 г.

2. Кораблев Н.М., Саранча С.Н., Саранча О.Н. - Методические указания к лабораторным работам по дисциплине «Компьютерная схемотехника»: Часть 2 «Проектирование сложных систем» - Харьков: ХНУРЭ, 2006 г.

3. Бибило П.Н. Синтез логических схем с использованием языка VHDL. - М.: СЛОН-Р, 2002. - 384 с.

4. http://vhdl - 1 .ru/

5. http://www.vhdl - 1 .ru/compon.html

6. http://www.bsuir.by/vhdl/index.php ? s ection=main

Приложение 1

VHDL-модель операционного автомата

use IEEE.STD_LOGIC_1164.all;

clk, rst: in STD_LOGIC;

d3: in STD_LOGIC;

r: out STD_LOGIC_VECTOR (15 downto 0);

x: out STD_LOGIC_VECTOR (4 downto 0)

architecture arch of OA_M is

Объявление внутренних сигналов

signal A, B, Arg2: STD_LOGIC_VECTOR (7 downto 0);

signal CF: STD_LOGIC_VECTOR (8 downto 0);

signal C, Arg1, Z: STD_LOGIC_VECTOR (15 downto 0);

signal Cnt: INTEGER;

signal COP: STD_LOGIC;

Сигналы A, B, C, COP - входы соответствующих регистров

Сигналы Arg1, Arg2 - шины аргументов

Сигнал Cnt - счётчик

process (clk, rst) is

Асинхронный сброс

A<=(others=>"0");

B<=(others=>"0");

C<=(others=>"0");

elsif rising_edge(clk) then

Синхронная записаь в регистр А

if y(1)="1" then A<=d1;

Синхронная записаь в регистр В

if y(2)="1" then B<=d2;

elsif (y(7) or y(12))="1" then B<=Z (7 downto 0);

Синхронная записаь в регистр С

if y(3)="1" then C<=(others=>"0");

elsif (y(6) or y(8) or y(11))="1" then C<=Z;

Синхронная запись результата

if y(10)="1" then r<=C (7 downto 0)&B (7 downto 0);

elsif y(13)="1" then r<=C;

Синхронная запись в счетчик

if y(4)="1" then Cnt<=8;

elsif y(9)="1" then Cnt<=Cnt-1;

Синхронная запись в регистр СОР

if y(5)="1" then COP<=d3;

else COP<="0";

Шина аргумента 1

arg1<= C when (y(6) or y(7) or y(8) or y(11))="1"

else (others=>"0");

Шина аргумента 2

arg2<= A when y(6)="1"

else B when (y(7) or y(12))="1"

else (others=>"0");

Формирование флага переноса

CF<=("0"&A (7 downto 0))+("0"&B (7 downto 0)) when y(8)="1";

Шина результата

Z<=Arg1 (15 downto 0)+arg2 (7 downto 0) when y(6)="1"

else «00000000»&Arg1 (0)&Arg2 (7 downto 1) when y(7)="1"

else «00000000»&CF(8)&Arg1 (7 downto 1) when y(8)="1"

else Arg1 (14 downto 0)&"0" when y(11)="1"

else «00000000»&Arg2 (6 downto 0)&"0" when y(12)="1"

else (others=>"0");

Формирование признаков результата

x(2)<="1" when B(0)="1" else "0";

x(3)<="1" when Cnt=0 else "0";

x(4)<="1" when B(7)="1" else "0";

Приложение 2

VHDL-модель управляющего автомата

use IEEE.STD_LOGIC_1164.all;

entity ua_mili is

clk: in STD_LOGIC; - вход синхронизации

rst: in STD_LOGIC; - вход сброса

x: in STD_LOGIC_VECTOR (4 downto 1); - входы логических условий

y: out STD_LOGIC_VECTOR (13 downto 1) - выходы микроопераций

architecture arch of ua_mili is

type TState is (a0, a1, a2, a3, a4, a5, a6, a7, a8); - множество внутренних состояний

signal State: TState;

process (clk, rst) is - функция переходов

if rst="0" then state<=a0;

elsif rising_edge(clk) then

when a0=>state<=a1;

when a1=>state<=a2;

when a2=>if x(1)="1" then state<=a3;

else state<=a6;

when a3=>state<=a4;

when a4=>state<=a5;

when a5=>if x(3)="1" then state<=a0;

else state<=a3;

when a6=>state<=a7;

when a7=>state<=a8;

when a8=>if x(3)="1" then state<=a0;

else state<=a6;

process(state) is - функция выходов

y<= «0000000000000»;

when a0=>y(1)<="1"; y(2)<="1"; y(3)<="1"; y(4)<="1";

when a1=>y(5)<="1";

when a2=>if x(1)="1" then

if x(2)="1" then y(6)<="1";

else y(11)<="1";

when a3=>y(7)<="1";

when a4=>y(8)<="1"; y(9)<="1";

when a5=>if x(3)="1" then y(10)<="1";

else if x(2)="1" then y(6)<="1";

when a6=>if x(4)="1" then y(6)<="1";

when a7=>y(9)<="1"; y(12)<="1";

when a8=>if x(3)="1" then y(13)<="1";

else y(11)<="1";

architecture struct of ua_mili is

signal D, Q:std_logic_Vector (3 downto 0); - входы и выходы регистра состояния

signal a0, a1, a2, a3, a4, a5, a6, a7, a8:STD_LOGIC;

process (clk, rst) is - процесс описывает 4-хразрядный регистр

if rst ="0"then Q<= «0001»;

elsif rising_edge(clk) then

Дешифратор состояний

a0<=(not Q(3)) and (not Q(2)) and (not Q(1)) and Q(0);

a1<=Q(3) and (not Q(2)) and (not Q(1)) and (not Q(0));

a2<=(not Q(3)) and (not Q(2)) and Q(1) and Q(0);

a3<=(not Q(3)) and (not Q(2)) and (not Q(1)) and (not Q(0));

a4<=(not Q(3)) and Q(2) and Q(1) and (not Q(0));

a5<=(not Q(3)) and Q(2) and (not Q(1)) and Q(0);

a6<=(not Q(3)) and (not Q(2)) and Q(1) and (not Q(0));

a7<=(not Q(3)) and Q(2) and (not Q(1)) and (not Q(0));

a8<=(not Q(3)) and Q(2) and Q(1) and Q(0);

Функции возбуждения триггеров

D(0)<=a1 or a4 or (a5 and x(3)) or a7 or (a8 and x(3));

D(1)<=a1 or (a2 and not x(1)) or a3 or a7 or (a8 and not x(3));

D(2)<=a3 or a4 or (a6 and x(4)) or (a6 and not x(4)) or a7;

Функции выходов

y(1)<=a0; y(2)<=a0; y(3)<=a0; y(4)<=a0; y(5)<=a1;

y(6)<=(a2 and x(1) and x(2)) or (a5 and not x(3) and x(2)) or (a6 and x(4));

y(7)<=a3; y(8)<=a4; y(9)<=a4 or a7; y(10)<=a5 and x(3);

y(11)<=(a2 and not x(1)) or (a8 and not x(3));

y(12)<=a7; y(13)<=a8 and x(3);

Приложение 3

VHDL-модель процессорного устройства

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_unsigned.all;

clk, rst: in STD_LOGIC;

d1: in STD_LOGIC_VECTOR (7 downto 0);

d2: in STD_LOGIC_VECTOR (7 downto 0);

d3: in STD_LOGIC;

r:out STD_LOGIC_VECTOR (15 downto 0)

architecture PM of PM is

Компонент - операционный автомат типа М

component OA_M is

clk, rst: in STD_LOGIC;

y: in STD_LOGIC_VECTOR (13 downto 1);

d1: in STD_LOGIC_VECTOR (7 downto 0);

d2: in STD_LOGIC_VECTOR (7 downto 0);

d3: in STD_LOGIC;

r:out STD_LOGIC_VECTOR (15 downto 0);

x: out STD_LOGIC_VECTOR (4 downto 1)

Компонент - управляющий автомат с жесткой логикой типа Мили

component ua_mili is

clk, rst: in STD_LOGIC;

x: in STD_LOGIC_VECTOR (4 downto 1);

y: out STD_LOGIC_VECTOR (13 downto 1)

Сигналы, которыми обмениваются ОА и УА.

signal y: STD_LOGIC_VECTOR (13 downto 0);

signal x: STD_LOGIC_VECTOR (3 downto 0);

OA: OA_M port map (clk, rst, y (13 downto 1), d1, d2, d3, r, x);

UA: ua_mili port map (clk, rst, x, y (13 downto 1));

Размещено на Allbest.ru

Подобные документы

Электронная система, реализующая сложный алгоритм обработки данных. Общая структура устройства управления. Проектирование процессорного модуля. Основные операционные элементы. Общие вопросы функционирования устройств управления с программируемой логикой.

курсовая работа , добавлен 29.06.2011

Расчет статического модуля оперативной памяти и накопителя. Построение принципиальной схемы и временной диаграммы модуля оперативного запоминающего устройства. Проектирование арифметико-логического устройства для деления чисел с фиксированной точкой.

курсовая работа , добавлен 13.06.2015

Изучение основных структурных элементов компьютера - электронного устройства, которое выполняет операции ввода информации, хранения и ее обработки по определенной программе. Функции центрального процессора, запоминающего устройства, носителей информации.

реферат , добавлен 18.01.2012

Анализ выбора цифрового сигнального процессора и структурной схемы устройства обработки информации. Расчет надежности устройства и производительности обмена данных, разработка ленточного графика. Обзор особенностей радиального и межмодульного интерфейса.

дипломная работа , добавлен 20.05.2012

Основные операции с матрицами. Проектирование объектно-ориентированного модуля для работы с матрицами в среде Delphi 7. Разработка программы, которая позволяет выполнять различные действия над матрицами. Описание интерфейса программы, исходный код модуля.

курсовая работа , добавлен 15.01.2013

Разработка условного графического обозначения элемента схемы. Разработка посадочного места, типового компонентного модуля. Формирование технического задания. Макетирование отдельных узлов и устройства. Разработка схемы электрической принципиальной.

методичка , добавлен 26.01.2009

Выбор принципов проектирования устройства записи, хранения и передачи чисел. Разработка алгоритма выполнения операций, необходимых для обработки информации. Структурная схема устройства. Элементарная база, необходимая для разработки принципиальной схемы.

Алгоритм выполнения операций, необходимых для обработки информации. Расчет и составление временной диаграммы управляющих сигналов. Выбор элементной базы, необходимой для разработки принципиальной схемы. Обнаружение ошибок, допущенных при вводе информации.

курсовая работа , добавлен 16.08.2012

Разработка модуля для вычисления значения функции, который впоследствии подключается к программе ввода исходных данных с контролем допусимого значения в таблицу. Проектирование модуля для работы со строками и для обработки массивов текстовой информации.

курсовая работа , добавлен 24.09.2010

Клавиатура как основное устройство ввода данных. Устройства манипуляторного типа, их виды и характеристики. Принципы действия сканеров. Предназначение графических планшетов. Устройства вывода информации, виды мониторов. Внешние хранители информации.

В качестве модуля управления, центрального процессораили процессорного модуля (CPU) понимается модуль ПЛК, выполняющий функции управления процессом, обработку прикладных программ, доступ к периферийным модулям, контроль/управление всей системой, функции управления логикой ПЛК и функции коммуникаций (обмен информацией через интерфейс программировании, а также для обмен данными с другими интеллектуальными устройствами системы автоматизации).

Рисунок 2.2 - Типовая архитектура ПЛК

При работе процессор "читает" входные данные с подключенных полевых устройств с помощью своих входных интерфейсов, и затем выполняет управляющую программу, которая загружена в память процессорного модуля. Программы обычно разрабатываются на специальных языках программирования ПЛК и должны быть загружены в память контроллера до начала его работы.

Наконец, на основании программы ПЛК "записывает" или обновляет управляющие выходы через выходные интерфейсы. Этот процесс, называемый циклом сканирования, постоянно выполняется в одной и той же последовательности без остановки и изменяется или при возникновении определенных, заранее оговоренных событий, или когда вносятся изменения в управляющую программу.

Процессорный модуль включает в себя микропроцессор (центральное процессорное устройство - ЦПУ), запоминающие устройства, часы реального времени и сторожевой таймер. Термины "микропроцессор" и "процессор" в настоящее время стали синонимами, поскольку все вновь выпускаемые процессоры выполняются в виде СБИС, т.е. являются микропроцессорами.

Основными характеристиками микропроцессора являются разрядность (в ПЛК используются 8-ми, 16-ти и 32-разрядные микропроцессоры), тактовая частота, архитектура, наличие операций с плавающей точкой, типы поддерживаемых портов ввода-вывода, температурный диапазон работоспособности и потребляемая мощность.

Производительность микропроцессоров с одной и той же архитектурой пропорциональна тактовой частоте. Большинство контроллеров используют микропроцессоры с сокращенным набором команд (RISC - Reduced Instruction Set Computing), в которых используется небольшое количество команд одинаковой длины и большое количество регистров. Сокращенный набор команд позволяет строить более эффективные компиляторы и конвейер процессора, способный за каждый такт выдавать результат исполнения очередной команды.

Для контроллеров, выполняющих интенсивную математическую обработку данных, важно наличие математического сопроцессора (вспомогательного процессора, выполняющего операции с плавающей точкой) или сигнальных процессоров, в которых операции типа Y=A*B+X выполняются за один такт. Сигнальные процессоры позволяют ускорить выполнение операций свертки или быстрого преобразования Фурье.

Емкость памяти определяет количество переменных (тегов), которые могут быть обработаны в процессе функционирования ПЛК. В микропроцессорах время доступа к памяти является одним из существенных факторов, ограничивающих быстродействие. Поэтому память делят на несколько уровней иерархии, в зависимости от частоты использования хранящихся в ней данных и быстродействия. Иерархия памяти относится к существенным характеристиками архитектуры процессора, поскольку она позволяет снизить отрицательное влияние медленной памяти на быстродействие микропроцессора. Основными типами памяти является постоянное запоминающее устройство (ПЗУ), оперативное запоминающее устройство (ОЗУ) и набор регистров. Регистры являются самыми быстродействующими элементами памяти, поскольку они используются арифметико-логическим устройством (АЛУ) для исполнения элементарных команд процессора. ПЗУ используют для хранения редко изменяемой информации, такой, как операционная система, драйверы устройств, загрузчик, исполняемый модуль программы пользователя. ОЗУ используется для хранения данных, которые многократно изменяются в процессе работы контроллера, например, значения тегов, результаты промежуточных вычислений, диагностическая информация, массивы, выводимые на графики, данные для отображения на дисплее.

В качестве ПЗУ (или ROM - "Read Only Memory") обычно используется электрически стираемая перепрограммируемая память (EEPROM - "Electrically Erasable Programmable ROM". Разновидностью EEPROM является флэш-память, принцип действия которой основан на хранении заряда в конденсаторе, образованном плавающим затвором и подложкой МОП-транзистора. Особенностью флэш-памяти является ее энергонезависимость, т.е. сохраняемость данных при выключенном питании. Стирание и перезапись во флэш-памяти выполняется не отдельными ячейками, а большими блоками, поэтому она получила название, происходящее от английского "flash" - "вспышка" . Недостатком всех ПЗУ является низкое быстродействие.

В качестве ОЗУ современные микропроцессоры используют статическую память (SRAM - Static Random Access Memory) и динамическую (DRAM - "Dynamic Random Access Memory"), SDRAM ("Synchronous DRAM"). SRAM выполняется на триггерах, информация в которых сохраняется неограниченно долго при наличии питания. В динамической памяти информация хранится на конденсаторах и поэтому DRAM требует периодической регенерации (перезарядки конденсаторов). К недостаткам триггерной памяти относится ее высокая стоимость, связанная с низкой плотностью компоновки триггеров на кристалле, и малое отношение емкости к цене. Достоинством является высокое быстродействие, достигающее гигагерц, в то время как память на конденсаторах не может работать на частотах выше сотен герц. Оба типа памяти (DRAM и SRAM) не могут сохранять информацию при отключении питания ПЛК. Поэтому некоторые типы ПЛК используют батарейное питание памяти для сохранения работоспособности системы автоматизации после кратковременного прерывания питания.

Моноблочные и модульные контроллеры используют, как правило, параллельную шину для обмена данными с модулями ввода-вывода, что позволяет на порядок повысить быстродействие их опроса по сравнению с последовательной шиной. Параллельные шины могут быть стандартными (ISA, PC/104, PCI, ComactPCI, VME, CXM) или частнофирменными. Последовательная шина контроллера (на основе интерфейса RS-485) используется для подключения к нему удаленных (распределенных) модулей ввода-вывода.

Сторожевой таймер (Watchdog Timer - WDT) представляет собой счетчик, который считает импульсы тактового генератора и в нормальном режиме периодически сбрасывается (перезапускается) работающим процессором. Если процессор "зависает", то сигналы сброса не поступают в счетчик, он продолжает считать и при достижении некоторого порога вырабатывает сигнал "Сброс" для перезапуска "зависшего" процессора.

Часы реального времени (РВ) представляют собой кварцевые часы, которые питаются от батарейки и поэтому продолжают идти при выключенном ПЛК. Часы РВ используются, например, для управления уличным освещением в зависимости от времени суток, в системах охраны объектов и других случаях, когда необходима привязка данных или событий к астрономическому времени.

Cтраница 1

Процессорные модули управляют дисплеями, клавиатурами, устройствами внешней памяти, выполняют расчеты, производят архивацию технологических и системных данных. Управляющие процессорные модули представляют собой контроллеры, реализующие совместно с модулями УСО функции регулирования, последовательного и логического управления.

Процессорные модули объединяются с несколькими модулями памяти и ввода-вывода. Это позволяет обеспечить необходимую живучесть за счет введения избыточных блоков и гибкость, т.е. возможность компоновки системы с учетом специфики применения. В СП применяется единая система адресации: для всей памяти и устройств ввода-вывода используется единое адресное поле.

Процессорные модули могут строиться на базе 8 - и 16-разрядных микропроцессоров.

Если процессорный модуль реализован в виде одной БИС, а схемы памяти и другие блоки реализованы на других БИС комплекта, то такую микропроцессорную систему называют функционально законченным микропроцессором с фиксированной разрядностью. Такой микропроцессор изображен на рис. 13.23. Возможна также ре1лизация процессорного модуля в виде нескольких БИС, при этом сам ЦП выполняемся в виде набора модулей определенной разрядности, а БИС, реализующая устройство управления - отдельно. МПБИС, в котором разрядность самого ЦП зависит от числа используемых арифметическо-логических БИС.

| ЭВМ с общей шиной. |

Поскольку процессорный модуль должен обмениваться данными с определенными ячейками памяти запоминающих устройств или с определенными портами, то для возможности обращаться (адресоваться) к ним, каждая ячейка памяти и каждый порт ввода и вывода имеют свои индивидуальные номера - адреса. При обмене данными процессорный модуль устанавливает двоичный код, соответствующий адресу порта или ячейки памяти на шине адреса ЭВМ.

При работе процессорный модуль должен обмениваться данными с периферийными модулями и ячейками памяти. Для того чтобы иметь такую возможность, каждые периферийный модуль и ячейка памяти имеют свои индивидуальные номера - адреса. По линии 3 рис. 13.23 производится подача управляющего сигнала на чтение из памяти; по линии 4-запись в память; по линиям / и 2 соответственно чтение и запись из устройства ввода-вывода. Одновременно через внутреннюю управляющую линию в микропроцессоре производится подача управляющих сигналов на РА памяти. В результате или на 16 линиях шины адресов появляется двоичный код, соответствующий адресу ячейки памяти, или на 8 линиях шины младших разрядов РА, соответствующий одному из портов ввода-вывода. Этот код по линиям шины адресов поступает на дешифраторы адреса памяти и адреса устройства ввода - вывода.

Система содержит процессорный модуль на МП КР580ИК80А со схемами формирования системной тины, к которой подключаются все внешние модули (блок приоритетных прерываний на БИС КР580ВН59, модуль ОЗУ-ПЗУ, модуль параллельного вывода и ввода на БИС К.

При работе процессорный модуль должен обмениваться данными с периферийными модулями и ячейками памяти. Для того чтобы иметь такую возможность, каждые периферийный модуль и ячейка памяти имеют свои индивидуальные номера - адреса. По линии 3 (см. рис. 16.2) производится подача управляющего сигнала на чтение из памяти; по линии 4 - запись в память; по линиям In 2 - соответственно чтение и запись из устройства ввода-вывода. Одновременно через внутреннюю управляющую линию в микропроцессоре производится подача управляющих сигналов на РА памяти. В результате двоичный код, соответствующий адресу ячейки памяти, появляется или на 16 линиях шины адресов, или на восьми линиях шины младших разрядов РА - соответствующий одному из портов ввода-вывода. Этот код по линиям шины адресов поступает на дешифраторы адреса памяти и адреса устройства ввода-вывода. Одновременно одной из четырех линий шины управления на устройство ввода-вывода или памяти поступает сигнал, разрешающий чтение или запись информации по заданному адресу.

Какую роль выполняет процессорный модуль.

| Структурная схема микропроцессорной системы. |

АЛУ определяются архитектурой процессорного модуля и микропроцессорной системы в целом. Типичными операциями, выполняемыми АЛУ большинства микропроцессорных систем, являются: СЛОЖЕНИЕ, ВЫЧИТАНИЕ, И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, ИНВЕРСИЯ, СДВИГ ВПРАВО, СДВИГ ВЛЕВО, ПРИРАЩЕНИЕ ПОЛОЖИТЕЛЬНОЕ, ПРИРАЩЕНИЕ ОТРИЦАТЕЛЬНОЕ.

В КОМГЛект МПБИГ кроме собственно процессорного модуля и памяти входят вспомогательные периферийные БИС. Схемные решения периферийных БИС таковы, чтз позволяют уменьшить общее число микросхем во всей микропроцессорной системе и тем способствуют снижению ее стоимости. В частности, периферийные устройства берут на себя выполнение части алгоритма функционирования аппаратуры параллельно с процессорным модулем и в результате увеличивают его производительность. Периферийные БИС обычно реализуют те функции, выполнение которых модулем невозможно или неэффективно.

Часто при построении ЭВМ для связи процессорного модуля с периферийными используется одна группа шин. В этом случае МП обращается к внешним устройствам ввода-вывода как к элементу памяти.

Услышать слова «встраиваемая система» в разговорах вокруг нас удается весьма редко, а если и удается, то, скорее всего, это разговоры специалистов (или тех, кто считает себя таковыми). Видимо, это как-то связано с особенностями «великого и могучего», потому как на самом-то деле эти «встраиваемые системы» сопровождают нас достаточно давно - первой подобной системой был компьютер, установленный на борту космического корабля «APPOLO 11», всемирно известного по совсем другой причине.

Итак, давайте вспоминать и размышлять. Как утверждают весьма компетентные источники, встраиваемая система (Embedded system) - это специализированная компьютерная система, полностью инкапсулированная в устройство, которым она управляет. Если читатель не против, будем пользоваться далее именно этим определением. Собственно встраиваемые системы можно поделить на два основных типа (сознательно жертвую деталями для подчеркивания сути).

Первый тип - микроконтроллерные системы. Строятся на базе специализированной микросхемы (или нескольких микросхем), выполняют одну-две-три вполне определенные функции. Ярчайший пример - современный телевизор: процессор обработки различных видеоформатов и собственно настройки телевизора, процессор обработки стереозвука, подсистема обработки телетекста. Вроде ничего не забыл?.. Работают они все по заранее заложенной программе (firmware) и перепрограммированию поддаются с большим трудом, а то и не поддаются вовсе. Кроме телевизора можно привести еще массу устройств со встраиваемой системой этого типа - пейджер, сотовый телефон, сканер, стиральная машина. Да в одном инжекторном автомобиле (а в иномарке - тем более) можно насчитать несколько десятков таких устройств - контроллер впрыска, контроллер АBS, контроллер курсовой устойчивости...

Второй тип - микропроцессорные системы. В отличие от систем первого типа, строятся на базе микропроцессоров, применяемых в обычных персональных компьютерах. Даже структура этих систем часто напоминает структуру персоналки. Есть, правда, разница - зачастую встраиваемые системы лишены некоторых деталей, в которых они не нуждаются в силу специфичности решаемой задачи. Согласитесь - цифровому фотоаппарату не зачем иметь мощную видеокарту с 3D-ускорителем. Ну вот, проговорился раньше времени... Ну да ладно, все равно пришлось бы об этом сказать. В чем же основное отличие систем этого типа? Вариантов ответа может быть несколько, но есть пара главных: во-первых, это перепрограммируемые системы. Во-вторых, это более-менее легко перепрограммируемые системы, ибо они программно совместимы с компьютерами, для которых уже написана масса программного обеспечения и на которых это программное обеспечение пишется. Примеры систем этого типа приводить несколько сложнее по причине их меньшей распространенности в обиходе: большинство бытовых DVD-проигрывателей, уже упомянутые цифровые фотоаппараты, автомобильные компьютеры (подчеркиваю - не простейшие маршрутные компьютеры, которые относятся к первому типу, а серьезные компьютеры под управлением Windows Automotive, с GPS, MPEG2 и т. п.), КПК, наладонники и почти все то, что связано с нишей PDA (Personal Digital Assistant), а также разные экзотические устройства типа холодильника с выходом в Internet...

Наибольшее распространение встраиваемые системы второго типа получили в промышленности, ибо их применение снижает время разработки, упрощает обслуживание и прочая, и прочая... Не буду перечислять здесь все преимущества - их можно найти практически в любой литературе на эту тему. Именно по этим причинам современные методы автоматизации немыслимы без использования подобных систем. Естественно, спрос рождает предложение. Что мы и имеем сегодня: немалое количество стандартов на «кирпичики» для создания встраиваемых систем и еще большее количество фирм, выпускающих эти самые «кирпичики». Посудите сами: только в Консорциуме PC/104 (организации, объединяющей фирмы-изготовители плат указанного стандарта) сейчас больше 200 участников. А если взять еще и PC/104Plus, CPCI, VME? Сотни изготовителей, тысячи наименований продукции. И все это для удобства разработчиков рынка встраиваемых систем.

Но закон сохранения энергии еще никто не отменил (хотя были попытки), и за эти преимущества нужно платить. Причем в прямом смысле - зачастую микропроцессорная система дороже микроконтроллерной. И в процессе разработки новой встраиваемой системы приходится решать некое экономическое уравнение. Переменных, входящих в это уравнение, не так много - стоимость разработки устройства на микроконтроллере или покупка готовой микропроцессорной платы, стоимость разработки программного обеспечения или стоимость написания firmware, стоимость обслуживания любой из систем, время ее жизни и возможность ее модернизации в это время. Уравнение получается достаточно сложное, и решается оно далеко неоднозначно. Скажем, кассовые аппараты обычно делают на микроконтроллере, а игровые автоматы - на микропроцессоре. Но бывает и наоборот!

Как вы понимаете, стоимость готовой платы играет далеко не последнюю роль при решении подобного уравнения. А если кроме привлекательной цены в активах этой платы имеется удобная среда разработки программного обеспечения, хорошая техническая поддержка со стороны изготовителя, возможность вносить аппаратные изменения в готовое устройство - выбор будет очевиден. Как вы уже поняли, вот так мягко и незатейливо я пытаюсь перевести разговор именно на микропроцессорные системы. Да что уж там скрывать - на продукцию одного разработчика!

Историческая справка

Компания CompuLab Ltd. (Израиль) была основана в 1992 году и начала свою деятельность с консультаций в области инженерных решений в электронике. В последующие пять лет компания принимает участие в нескольких десятках заказных разработок. Накопленный опыт, деловая активность, изучение рынка и высочайший инженерный потенциал позволили CompuLab Ltd. в достаточно короткие сроки заняться проектированием собственной продукции. В 1997 году компания выпускает собственную разработку - семейство процессорных модулей CORE. К сожалению, несмотря на инновационность технических и инженерных решений, заложенных в первое поколение модулей, архитектура используемого в них процессора (i960) не оправдала надежд разработчиков на широкое внедрение.

Второе поколение модулей увидело свет в 1999 году. Эти модули базировались на процессоре AMD ELAN SC400 (архитектура х86) и назывались 486CORE. На тот момент это были самые маленькие в мире компьютеры. Фантастический успех 486CORE на рынке подтвердил правильность выбранной стратегии. С тех пор семейство модулей CORE неоднократно пополнялось и, смеем надеяться, будет расти и в дальнейшем.

Сочетание большой вычислительной мощности и малых габаритов модулей способствовало быстрому завоеванию рынка встраиваемых систем. Сегодня продукцией компании CompuLab пользуется более 300 фирм в 50 странах мира, а сама компания производит почти 20% продукции этого рынка. Среди основных покупателей этих модулей можно упомянуть таких известных гигантов, как Cisco Systems, Marconi, General Electric, OKI и многих других производителей, не так широко известных в России.

Спектр применений модулей CORE весьма широк: военная и авиационная промышленность, медицинская техника, транспорт, телекоммуникационное оборудование, интеллектуальные сетевые устройства, мини-компьютеры, компьютерная периферия, оборудование для индустрии развлечений...

Техническая справка № 1

Процессорные модули CompuLab Ltd. - это полнофункциональные вычислительные системы с оперативной памятью, встроенными Flash-дисками, контроллером Ethernet, поддержкой стандартной для настольных компьютеров периферии и другими красивыми и полезными мелочами, которые так упрощают жизнь разработчику. Все необходимые для их работы электрические линии выведены на унифицированные компанией разъемы (CAMI - CompuLab"s Aggregated Module Interface) и предназначены для стыковки с соответствующей платой-носителем (обычно формата PC/104). Платы эти могут содержать (а могут и не содержать - об этом позднее) следующие устройства: преобразователь питания, шинные формирователи последовательных портов, шины PC/104 и PC/104 Plus, дополнительный контроллер Ethernet, контроллер PCMCIA и пр. Будучи соединенными вместе, плата-носитель и процессорный модуль образуют компьютер с возможностями, идентичными обычному ПК, но гораздо меньших габаритов.

Искушенный читатель может поглумиться над этими строчками, потому как ничего нового в этом описании нет. А вот сейчас - самое интересное: на платы-носители есть электрическая схема и даже рекомендации по разводке собственных плат-носителей. Ну как? Впечатляет? Достаточно сделать свою плату и поставить в нее готовое вычислительное ядро - и все! Нужен игровой автомат - пожалуйста, нужен бортовой накопитель (в каком-нибудь форм-факторе типа ARINC-429) - пожалуйста! Нет предела совершенству! Кстати, именно так и поступает большая часть заказчиков компании CompuLab.

Все, не буду больше мучить туманными фразами. Последующая часть статьи содержит более подробное описание продукции. Сразу предупреждаю: если вы, уважаемый читатель, уже знакомы с этими платами - не читайте дальше. Цифры и технические термины на английском языке вгоняют в хандру...

Техническая справка № 2

В 2005 году компания изменила наименование своей продукции, поэтому далее будем пользоваться только новыми определениями. Таблица с сайта изготовителя приводится здесь с небольшими сокращениями и комментариями:

- Кроме указанных опций, все модули имеют в своем составе шину PCI, часы реального времени, интерфейсы жесткого диска и звуковой кодек.

- Высота модулей указана без радиатора.

- Производительность замерялась тестом SiSoft Sandra.

- В таблице приведены данные только на новые и самые популярные модули. Где можно получить более подробную информацию, сообщу позднее.

Таблица. Характеристики вычислительных модулей CompuLab Ltd.

Как вы могли заметить, наряду с более привычной всем архитектурой х86 в списке продукции присутствуют и изделия на процессорах типа RISC. Первоначально данная статья планировалась как обзор СМ-Х255 (модуль СМ-Х270W был анонсирован во время ее написания), поэтому с этой платы и начнем. Сразу хочу внести ясность - версий модуля СМ-Х255 существует две (2.0 и версия 3.0, называемая также «GX»), речь пойдет только о последней.

Структурная схема модуля представлена на рис. 1. Обратите внимание на позиции, отмеченные строчкой «opt». Это как раз и есть заказные позиции («option») в конфигурации процессорной платы, которые могут устанавливаться (или сниматься) по желанию заказчика.

Рис. 1. Структурная схема модуля СМ-Х225

Теперь - обзор основных составляющих этой платы. Думаю, что логично будет начать с процессора. Итак - Intel XScale PXA255. В принципе, только ему можно было посвятить весь номер этого журнала, но так как речь не только о нем, то постараюсь быть кратким:

- Кристалл процессора изготовлен по 0,18-микронной технологии, что обеспечивает низкое энергопотребление при высокой тактовой частоте (400 МГц).

- Процессор совместим с архитектурой ARM v.5TE.

- Intel Media Processing Technology (включая 40-битный аккумулятор и операцию 16-битного умножения) ускоряет декодирование аудио/видеопотоков.

- Кроме собственно вычислителя в состав процессора входит поддержка PCMCIA/Compact Flash, 17 линий ввода/вывода общего назначения (GPIO), часы реального времени (RTC), сторожевой таймер (watchdog), контроллер управления питанием, контроллер прерываний, контроллер прямого доступа к памяти, контроллер аппаратного сброса (reset controller), графический контроллер с поддержкой ЖК-панелей, в том числе и TFT, три последовательных порта, Bluetooth, IrDA (SIR и FIR), I2C, I2S, AC97, SPI, USB, JTAG, контроллер MMC, два независимых тактовых генератора (32768 Гц и 3,6864 МГц).

- Процессор выпускается для обычного и расширенного температурных диапазонов.

Совсем уж как-то коротко получилось... Тем, кто ожидал большего, советую посмотреть список литературы в конце статьи.

Теперь чуть подробнее об остальных компонентах и характеристиках модуля (рис. 1).

Оперативная память типа SDRAM с 32-разрядной шиной и частотой 100 МГц.

Flash-диски двух типов - NOR и NAND. Первый мегабайт NOR используется для хранения программы-монитора (ARMMON), остальное - для хранения ядра Linux или загрузчика Windows CE. В состав ARMMON входит драйвер поддержки памяти NAND, что позволяет записывать туда файловую систему Linux или образ Windows CE. Оба диска имеют аппаратную защиту от записи (одна из линий разъема CAMI).

Interface Bridge представляет собой микросхему так называемого чипа-компаньона (companion chip), расширяющего возможности процессора. В состав этой микросхемы входят контроллер SDRAM, контроллер шины PCI (версия 2.1, частота 33 МГц), расширение контроллера прерываний, расширение контроллера прямого доступа к памяти, четырехканальный счетчик-таймер, контроллер шины LPC, два дополнительных канала USB (типа Host, 1,5–12 Мбит/с) и еще один последовательный порт.

Про контроллер Ethernet долго распространяться не буду: 10–100 Мбит/с.

Звуковой кодек и контроллер сенсорного экрана (touchscreen) расширяют возможности интерфейса AC97, заложенного в процессор. При установленном кодеке (Crystal CS4299 или UCB1400) у модуля появляется монофонический микрофонный вход, стереофонические линейный вход и выход. Часть микросхемы UCB1400 является контроллером четырехпроводного резистивного сенсорного экрана.

Микросхема Super-I/O. Возможно, специалисты могли бы сейчас снисходительно похлопать меня по плечу, заявив, что бывает и не такое. Возможно. Но, если честно, умел бы писать стихи - написал бы оду CompuLab за красоту инженерных решений. Одно из них - использование контроллеров типа Super-I/O. Это решение применяется во всех модулях, выпускаемых компанией, и сильно облегчает жизнь разработчикам. В данном случае на CM-X255 установлена микросхема IT8711F, поддерживающая следующие устройства: клавиатуру и мышь типа PS/2, параллельный порт (с возможностью подключения накопителя на гибких магнитных дисках) и еще один последовательный порт.

Еще один контроллер RTC (MAX6902) установлен на модуле для учета времени при выключенном процессоре .

Единственный формирователь линии RS-232 для последовательного порта (COM-A) установлен прямо на модуле. Этот порт выполняет роль консольного при работе с ARMMON, его же можно использовать для диагностики и отладки при работе в Linux иWindows CE.

Весьма сухую информацию о габаритах модуля (табл.) можно слегка оживить его фотографией (рис. 2). Два больших 180-контактных разъема на нем и есть упоминавшиеся ранее CAMI.

Рис. 2. Модуль СМ-Х225 - вид снизу

Теперь несколько слов о плате-носителе. Точнее - о платах-носителях, ибо для данного модуля их существует две разновидности. Начнем с меньшей по размерам.

Техническая справка № 3

Плата SB-X255 (старое название ARMBASE). Представляет собой носитель для CM-X255, выполненный в форм-факторе PC/104 (на рис. 3 SB-X255 показана с установленным на нее процессорным модулем). Жаль, что современные средства массовой информации пока не позволяют задействовать все органы чувств...

Процессорный модуль (Processor module) – это разновидность одноплатных компьютеров, относится к встраиваемым компьютерным системам. Представляет собой небольшой модуль, на котором расположены процессор, графический, сетевые и другие необходимые котроллеры, и который может устанавливается на базовую плату различных форм-факторов, как например, ATX или EPIC.

Наша компания поставляет следующие типы процессорных модулей:

Применение процессорных модулей в приборостроении привело к тому, что схемотехника плат упростилась, унифицировалась. Разработчикам стало легче подбирать основу для новых устройств и, следовательно, ускорился выпуск продукции на рынок.

Процессорные модули, благодаря своему многообразию и универсальности, нашли свое применение во многих отраслях:

- производство

- системы автоматизации

- медицина

- военно-промышленный комплекс

- авионика

- энергетика

- тестирование и измерение

Функциональные особенности процессорных модулей

Процессорные модули разделяются по типам ETX, COM-Express, QSeven, SOM, uProcessor и отличаются производительностью, низким энергопотреблением и тепловыделением, так как разработаны для встраиваемых применений, где задачи отвода тепла внутри компактного корпуса являются критичными при выборе типа модуля.

Основным преимуществом систем на процессорных модулях является как раз их модульная конструкция. В целом ряде применений не получается использовать платы стандартных форм-факторов, как например, 3.5” или EPIC, так как размеры платы ограничивают количество поддерживаемых интерфейсов ввода-вывода и не всегда можно вывести все необходимые разъемы на плате. Также со временем платы устаревают и найти подходящее решение к уже существующему корпусу становится очень не просто. Если же использовать процессорный модуль совместно с базовой платой, то здесь вы можете сами выбирать какие разъемы вам необходимо вывести на базовую плату, какого размера должна быть базовая плата и какой процессорный модуль (с каким процессором и чипсетом соответственно) использовать в вашей системе. Если же вы хотите улучшить производительность вашей системы и использовать более новые процессоры, например, то вы просто можете выбрать новый процессорный модуль соответствующего типа и установить его на используемую базовую плату.

Процессорный модуль надежно закрепляется на базовой плате, поэтому системы на основе модульной структуры отлично выдерживают вибрационные нагрузки. Именно этим и обусловлено применение их в военно-промышленном комплексе и авионике, где надежность и работоспособность имеют главенствующее значение.

Встраиваемые решения сегодня требуют не только высокой производительности, но также наличия большого числа портов ввода/вывода в компактном форм-факторе. Малые размеры, надежность, масштабируемость – все это преимущества процессорных модулей. Именно поэтому модульные компьютеры спецификаций COM Express, ETX и Qseven активно применяются на данный момент в различных промышленных и военных системах. Ассортимент компании IPC2U представлен процессорными модулями компаний IEI, ICOP, AXIOMTEK, NEXCOM, ADVANTECH и другими мировыми производителями.