Как происходит чтение из памяти dram. Виды модулей памяти и их характеристики

Динамическая оперативная память (Dynamic RAM - DRAM) используется в большинстве систем оперативной памяти современных персональных компьютеров. Основное преимущество этого типа памяти состоит в том, что ее ячейки упакованы очень плотно, т.е. в небольшую микросхему можно упаковать много битов, а значит, на их основе можно построить память большой емкости.

Ячейки памяти в микросхеме DRAM - это крошечные конденсаторы, которые удерживают заряды. Именно так (наличием или отсутствием зарядов) и кодируются биты. Проблемы, связанные с памятью этого типа, вызваны тем, что она динамическая, т.е. должна постоянно регенерироваться, так как в противном случае электрические заряды в конденсаторах памяти будут “стекать” и данные будут потеряны. Регенерация происходит, когда контроллер памяти системы берет крошечный перерыв и обращается ко всем строкам данных в микросхемах памяти. Большинство систем имеет контроллер памяти (обычно встраиваемый в набор микросхем системной платы), который настроен на соответствующую промышленным стандартам частоту регенерации, равную 15 мкс. Ко всем строкам данных обращение осуществляется по прохождении 128 специальных циклов регенерации. Это означает, что каждые 1,92мс (128x15 мкс) прочитываются все строки в памяти для обеспечения регенерации данных.

Регенерация памяти, к сожалению, "отнимает время" у процессора: каждый цикл регенерации по длительности занимает несколько циклов центрального процессора. В старых компьютерах циклы регенерации могли занимать до 10% (или больше) процессорного времени, но в современных системах, работающих на частотах, равных сотням мегагерц, расходы на регенерацию составляют 1% (или меньше) процессорного времени. Некоторые системы позволяют изменить параметры регенерации с помощью программы установки параметров CMOS, но увеличение времени между циклами регенерации может привести к тому, что в некоторых ячейках памяти заряд "стечет", а это вызовет сбои памяти. В большинстве случаев надежнее придерживаться рекомендуемой или заданной по умолчанию частоты регенерации.

3.3. Кэш-память - SRAM

Существует тип памяти, совершенно отличный от других, - статическая оперативная память (Static RAM - SRAM). Она названа так потому, что, в отличие от динамической оперативной памяти (DRAM), для сохранения ее содержимого не требуется периодической регенерации. Но это не единственное ее преимущество. SRAM имеет более высокое быстродействие, чем динамическая оперативная память, и может работать на той же частоте, что и современные процессоры.

Время доступа SRAM не более 2 нc, это означает, что такая память может работать синхронно с процессорами на частоте 500 МГц или выше! Однако для хранения каждого бита в конструкции SRAM используется кластер из шести транзисторов. Использование транзисторов без каких-либо конденсаторов означает, что нет необходимости в регенерации. (Ведь если нет никаких конденсаторов, то и заряды не теряются.) Пока подается питание, SRAM будет помнить то, что сохранено. Почему же тогда микросхемы SRAM не используются для всей системной памяти? Ответ можно найти в следующей таблице.1

|

Плотность |

Быстродейст- |

Стоимость |

|

|

Динамическая оперативная память - DRAM | |||

|

Статическая оперативная память - SRAM |

По сравнению с динамической оперативной памятью быстродействие SRAM намного выше, но плотность ее намного ниже, а цена довольно высокая. Более низкая плотность означает, что микросхемы SRAM имеют большие габариты, хотя их информационная емкость намного меньше. Большое число транзисторов и кластеризованное их размещение не только увеличивает габариты микросхем SRAM, но и значительно повышает стоимость технологического процесса по сравнению с аналогичными параметрами для микросхем DRAM. Например, емкость модуля DRAM может равняться 64 Мбайт или больше, в то время как емкость модуля SRAM приблизительно того же размера составляет только 2 Мбайт, причем их стоимость будет одинаковой. Таким образом, габариты SRAM в среднем в 30 раз превышают размер динамической оперативной памяти, то же самое можно сказать и о стоимости. Все это не позволяет использовать память типа SRAM в качестве оперативной памяти в персональных компьютерах.

Несмотря на это, разработчики все-таки применяют память типа SRAM для повышения эффективности PC. Но во избежание значительного увеличения стоимости устанавливается только небольшой объем высокоскоростной памяти SRAM, которая используется в качестве кэш-памяти. Кэш-память работает на тактовых частотах, близких или даже равных тактовым частотам процессора, причем обычно именно эта память непосредственно используется процессором при чтении и записи. Во время операций чтения, данные в высокоскоростную кэш-память предварительно записываются из оперативной памяти с низким быстродействием, т.е. из DRAM.

Еще недавно время доступа динамической оперативной памяти было не менее 60 нc (что соответствует тактовой частоте 16 МГц). Когда процессор персонального компьютера работал на тактовой частоте 16 МГц и ниже, DRAM могла быть синхронизирована с системной платой и процессором, поэтому кэш был не нужен. Однако, как только тактовая частота процессора поднялась выше 16 МГц, синхронизировать DRAM с процессором стало невозможно, и именно тогда разработчики начали использовать SRAM в персональных компьютерах. Это произошло в 1986 и 1987 годах, когда появились PC с процессором 386, работающим на частотах 16 и 20 МГц. Именно в этих персональных компьютерах впервые нашла применение так называемая кэш-память, т.е. высокоскоростной буфер, построенный на микросхемах SRAM, который непосредственно обменивается данными с процессором. Поскольку быстродействие кэша может быть сравнимо с быстродействием процессора, контроллер кэша может предугадывать потребности процессора в данных и предварительно загружать необходимые данные в высокоскоростную кэш-память. Тогда при выдаче процессором адреса памяти данные могут быть переданы из высокоскоростного кэша, а не из оперативной памяти, быстродействие которой намного ниже.

Эффективность кэш-памяти выражается коэффициентом совпадения , или коэффициентом успеха . Коэффициент совпадения равен отношению количества удачных обращений в кэш к общему количеству обращений. Попадание - это событие, состоящее в том, что необходимые процессору данные предварительно считываются в кэш из оперативной памяти; иначе говоря, в случае попадания процессор может считывать данные из кэш-памяти. Неудачным обращением в кэш считается такое, при котором контроллер кэша не предусмотрел потребности в данных, находящихся по указанному абсолютному адресу. В таком случае необходимые данные не были предварительно считаны в кэш-память, поэтому процессор должен отыскать их в более медленной оперативной памяти, а не в быстродействующем кэше. Когда процессор считывает данные из оперативной памяти, ему приходится какое-то время "ждать", поскольку тактовая частота оперативной памяти значительно ниже, чем процессора. Если процессор работает на частоте 233 МГц, то продолжительность его цикла равна примерно 4 нс, в то время как продолжительность цикла оперативной памяти может составлять 60 нс, что соответствует тактовой частоте 16 МГц. Таким образом, каждый раз, когда процессор считывает данные из оперативной памяти, его работа замедляется. Это настолько ощутимо, что кажется, будто он работает на тактовой частоте 16 МГц! Замедление обусловлено состоянием ожидания. Если процессор находится в состоянии ожидания, то на протяжении всего цикла (такта) никакие операции не выполняются; процессор, по существу, ждет, пока необходимые данные поступят из более медленной.оперативной памяти. Поэтому именно кэш-память позволяет сократить количество "простоев" и увеличить быстродействие компьютера в целом.

Чтобы минимизировать время ожидания при считывании процессором данных из медленной оперативной памяти, в современных персональных компьютерах обычно предусмотрены два типа кэш-памяти: кэш-память первого уровня (L1) и кэш-память второго уровня (L2). Кэш-память первого уровня также называется встроенным, или внутренним кэшем; он непосредственно встроен в процессор и фактически является частью микросхемы процессора. Во всех процессорах 486 и выше кэш-память первого уровня интегрирована в микросхему процессора.

Кэш-память второго уровня называется вторичным, или внешним кэшем; он устанавливается вне микросхемы процессора. Первоначально она устанавливалась на системной плате. (Так было во всех компьютерах на основе процессоров 386, 486 и Pentium.) Если кэш-память второго уровня установлена на системной плате, то она работает на ее частоте. В этом случае кэш-память второго уровня обычно находится рядом с разъемом процессора.

Для повышения эффективности в более поздних компьютерах на основе процессоров фирмы Intel, в том числе в Pentium Pro и Pentium II/III, кэш-память второго уровня является частью процессора. Конечно же, он внешний по отношению к кристаллу центрального процессора, просто эта отдельная микросхема устанавливается внутри корпуса (картриджа) процессора. Поэтому на системных платах для процессоров Pentium Pro или Pentium II нет никакого кэша.

В табл.2 приведены параметры кэш-памяти первого (внутреннего) и второго уровней (внешнего) в современных компьютерах.

3.4. RDRAM

RDRAM, или Rambus DRAM, является радикально новым типом памяти, который используется в высокопроизводительных персональных компьютерах с 1999 года. Такая память непосредственно поддерживается в наборах микросхем системной логики. Аналогичный тип памяти уже использовался в игровых приставках - в популярной модели Nintendo 64.

Обычные типы памяти (FPM/RDO и SDRAM) иногда называют системами с широким каналом. Ширина канала памяти равна ширине шины данных процессора (в системах Pentium 64-бит). Максимальная производительность памяти SDRAM в исполнении DIMM составляет 100x8 (частота x количество передаваемых данных за один такт), или 800 Мбайт/с.

Микросхемы RDRAM увеличивают пропускную способность памяти - в них предусмотрена "удвоенная" (16-разрядная) шина передачи данных, частота увеличена до 800 МГц, а пропускная способность равна 1,6 Гбайт/с. Для увеличения производительности можно использовать двух- и четырехканальные RDRAM, которые позволяют увеличить скорость передачи данных до 3,2 или 6,4 Гбайт/с соответственно.

0дин канал памяти Rambus может поддерживать до 32 отдельных устройств RDRAM (микросхем RDRAM), которые устанавливаются в модули RIMM (Rambus Inline Memory Modules). Вся работа с памятью организуется между контроллером памяти и отдельным (а не всеми) устройством. Каждые 10нс (100МГц) одна микросхема RDRAM может передавать 16 байт.

Таблица 2 Параметры кэш-памяти первого (внутреннего) и второго уровней (внешнего) в современных компьютерах

|

Тип центрального процессора |

Типичная тактовая частота центрального процессора, МГц |

Быстродействие кэш-памяти первого уровня, нс (МГц) |

Быстродействие кэш-второго уровня, нс (МГц) |

Быстродействие системной платы, (МГц) |

Быстродействие SIMM/DIMM, нс (МГц) |

|

Pentium II (1997) | |||||

|

Pentium II (1998) | |||||

|

Pentium III Xeon |

RDRAM работает быстрее SDRAM приблизительно в три раза.

Модули RIMM имеют посередине два ключа, которые, с одной стороны, предотвращают неправильную установку в разъем, а с другой - указывают рабочее напряжение. В настоящее время практически все модули RIMM имеют рабочее напряжение 2,5 В, однако вскоре должны появиться устройства с пониженным энергопотреблением. Для новых типов модулей предназначены дополнительные ключи (рис. 4). Один из ключей в модуле имеет фиксированное положение (он называется DATUM А), а тип используемого модуля указывает другой ключ, который расположен на некотором расстоянии (с приращением 1 или 2 мм) от первого ключа DATUM А. В настоящее время используются модули типа А (2,5 В). Параметры ключей и их назначение приведены в табл. 3.

Рисунок 3

Рисунок 4

Таблица 3. Параметры ключей модулей RIMM и их назначение

|

Расстояние от DATUM A , мм |

Описание |

|

|

Зарезервирован |

||

|

Зарезервирован |

В каждом модуле RIMM устанавливается микросхема Serial Presence Detect (SPD), которая представляет собой перезаписываемое постоянное запоминающее устройство. В нем хранится информация о размере и типе RIMM, включая более детальные сведения для контроллера памяти. Контроллер считывает эту информацию и конфигурирует с ее помощью установленную память.

На рис. 5 показана схема установки модуля RIMM. Котроллер RDRAM и тактовый генератор обычно устанавливаются на системной плате и являются частью компонента системной логики North Bridge. Как видите, три модуля RIMM подключаются последовательно к контроллеру памяти. Каждый модуль содержит 4, 8 или 16 микросхем RDRAM, а также микросхему SPD. Каждый новый модуль RIMM необходимо подключать непосредственно за последним установленным. В каждый пустой разъем необходимо установить модуль согласования (на рис. 5 он установлен в последний свободный разъем). Временные характеристики работы памяти накладывают ограничение на расстояние между первым модулем RIMM и контроллером памяти на системной плате - не более 6 дюймов (15,24мм). Общая длина шины не должна превышать расстояние, которое сигнал пройдет за четыре такта (около 5 нc).

На протяжении долгого времени разработчиками создавались различные типы памяти. Они обладали разными характеристиками, в них были использованы разные технические решения. Основной движущей силой развития памяти было развитие ЭВМ и центральных процессоров. Постоянно требовалось увеличение быстродействия и объёма оперативной памяти.

Страничная память

Страничная память (англ. pagemodeDRAM,PMDRAM) являлась одним из первых типов выпускаемой компьютерной оперативной памяти. Этот тип DRAM осуществляет чтение каждой ячейки памяти за 5 тактов. Каждая ячейка в обычной памяти читается/записывается независимо от другой. Память такого типа выпускалась в начале 90-х годов, но с ростом производительности центральных процессоров и ресурсоёмкости приложений требовалось увеличивать не только объём памяти, но и скорость её работы.

Быстрая страничная память

Быстрая страничная память (англ. fastpagemodeDRAM,FPMDRAM) появилась в 1995 году. Принципиально новых изменений память не претерпела. Отличие FPM от просто PM DRAM состоит в том, что введена укороченная схема считывания данных после первой ячейки, то есть первая ячейка будет считыватся за 5 тактов, а остальные - за 4.

Данный тип памяти в основном применялся для компьютеров с процессорами Intel486 или аналогичных процессоров других фирм. Память могла работать на частотах 25 МГц и 33 МГц с временем полного доступа 70 нс и 60 нс и с временем рабочего цикла 40 нс и 35 нс соотвественно.

Память с усовершенствованным выходом

Но с появлением процессоров IntelPentiumIIпамятьFPMDRAMоказалась совершенно неэффективной. Поэтому следующим шагом стала память с усовершенствованным выходом (англ.extendeddataoutDRAM,EDODRAM). Эта память появилась на рынке в 1996 году и стала активно использоваться на компьютерах с процессорамиIntelPentiumи выше. Её производительность оказалась на 10-15 % выше по сравнению с памятью типаFPMDRAM.

Схема считывание данных была еще укорочена, при этом достижимой стало считывание последующих за первой ячеек за 3 такта системной шины.

Её рабочая частота была 40 МГц и 50 МГц, соответственно, время полного доступа - 60 нс и 50 нс, а время рабочего цикла - 25 нс и 20 нс. Эта память содержит регистр-защелку (datalatch) выходных данных, что обеспечивает некоторую конвейеризацию работы для повышения производительности при чтении.

Синхронная DRAM

В связи с выпуском новых процессоров и постепенным увеличением частоты системной шины, стабильность работы памяти типа EDODRAMстала заметно падать. Ей на смену пришла синхронная память (англ.synchronousDRAM,SDRAM).

SDRAM синхронизирована с системным таймером, управляющим центральным процессором. Системные "часы" управляют работой SDRAM, уменьшая задержки в процессе ожидания и существенно сокращая время, требуемое на поиск данных в памяти.

Новыми особенностями этого типа памяти являлись также и использования конвейерной обработки информации. Также память надёжно работала на более высоких частотах системной шины (100 МГц и выше). Недостатками данного типа памяти явилась в то время его высокая цена, а также его несовместимость со многими чипсетами и материнскими платами в силу своих новых конструктивных особенностей. Рабочие частоты этого типа памяти могли равняться 66 МГц, 100 МГц или 133 МГц, время полного доступа - 40 нс и 30 нс, а время рабочего цикла - 10 нс и 7.5 нс.

Другое усовершенствование. Количество матриц (банков) памяти в SDRAMувеличено с одного до двух (а, в некоторых моделях, и четырех). Это позволяет обращаться к ячейкам одного банка параллельно с перезарядкой внутренних цепей другого, что вдвое увеличивает предельно допустимую тактовую частоту. Помимо этого появилась возможность одновременного открытия двух (четырех) страниц памяти, причем открытие одной страницы (т.е. передача номера строки) может происходить во время считывания информации с другой, что позволяет обращаться по новому адресу столбца ячейки памяти на каждом тактовом цикле.

В отличие от FPM-DRAM\EDO-DRAM\BEDO, выполняющих перезарядку внутренних цепей при закрытии страницы (т.е. при дезактивации сигналаRAS), синхронная память проделывает эту операцию автоматически, позволяя держать страницы открытыми столь долго, сколько это угодно.

Наконец, разрядность линий данных увеличилась с 32 до 64 бит, что еще вдвое увеличило ее производительность.

Пакетная EDO RAM

Пакетная память EDORAM(англ.burstextendeddataoutputDRAM,BEDODRAM) стала дешёвой альтернативой памяти типаSDRAM. Основанная на памятиEDODRAM, её ключевой особенностью являлась технология поблочного чтения данных (блок данных читался за один такт), что сделало её работу быстрее, чем у памяти типаSDRAM. Однако невозможность работать на частоте системной шины более 66 МГц не позволила данному типу памяти стать популярным.

Доступ к стандартной памяти DRAM осуществляется с помощью технологии под названием paging. Обычный доступ к памяти требует выбора адреса строки и столбца, что требует больших затрат времени.

Пейджинг обеспечивает более быстрый доступ ко всем данным в заданной строке памяти, сохраняя тот же адрес строки и изменяя только столбец. Использующая этот метод память, называется «Page Mode» или «Fast Page Mode». Другие вариации называния режима Page Mode - Static Column или Memory Mode.

Пейджинговая память - это простая схема повышения производительности памяти, которая делит память на «page» размером от 512 байт до нескольких килобайт. Схема пейджинга позволяет доступ к ячейкам памяти с меньшим количеством состояний ожидания. Если нужная ячейка памяти находится за пределами текущей page, при выборе системой новой страницы, добавляются одно или несколько состояний ожидания.

Чтобы повысить скорость доступа к памяти, системам понадобилось обеспечивать более быстрый доступ к DRAM. Одним из важных изменений стало внедрение в процессорах 486 и более поздних версий, режима пакетного доступа. Режим циклического переключения, при большинстве обращений к памяти, использует преимущества последовательности.

Используя режим пакетной обработки, после настройки для заданного доступа адресов строк и столбцов, вы можете получить доступ к следующим трём соседним адресам без дополнительных состояний ожидания. Обычно доступ к пакету ограничен четырьмя полными доступами. Чтобы описать это, мы часто ссылаемся на тайминг в количестве циклов для каждого доступа. Типичный пакетный режим доступа стандартной DRAM выражается как x-y-y-y. Где x - время для первого доступа (время задержки плюс время цикла), а y - количество циклов, необходимых для каждого последовательного доступа.

Стандартная 60-разрядная DRAM - память обычно работает с частотой 5-3-3-3 импульсов. Это означает, что первый доступ занимает в общей сложности пять циклов (на системной шине 66 МГц, это около 75ns, или 5 × 15ns циклов), а последовательные циклы занимают три цикла каждый (3 × 15ns = 45ns). Как вы можете видеть, фактический системный тайминг несколько меньше, чем технически рассчитана память.

Без технологического прерывания доступ к памяти будет 5-5-5-5, потому что для каждой передачи памяти необходима полная латентность. Время цикла 45ns во время пакетных передач равно примерно 22,2 МГц эффективной тактовой частоты. В системе с 64-битной (8-байтной) шиной памяти это приведёт к максимальной пропускной способности 177 Мбит/с (22,2 МГц × 8 байтов = 177 Мбит/с).

Память DRAM, поддерживает пейджинг, и этот метод разрыва называется памятью Fast Page Mode (FPM). Этот термин относится к возможности доступа к данным на одной и той же странице памяти быстрее, чем к данным на других страницах памяти.

Большинство систем 386, 486 и Pentium с 1987 по 1995 год использовали память FPM, которая включала в себя либо 30-контактную, либо 72-контактную форму SIMM.

Другой способ ускорения памяти FPM - чередование. В этой конструкции совместно используются два отдельных банка памяти, чередуя доступ из одного в другой, как чётный и нечётный байт. В то время как обращаются к одному, другой, когда выбираются адреса строк и столбцов, предварительно заряжается. К тому времени, когда первый в паре банк закончит возвращать данные, второй банк завершает цикл задержки и готов к возврату данных. Когда возвращает данные второй банк, заряжается, выбирая адрес строки и столбца следующего доступа, первый банк. Такое перекрытие доступа в двух банках уменьшает эффект задержки или циклов предварительной зарядки и позволяет ускорить общий поиск данных. Единственная проблема заключается в том, что для использования чередования необходимо установить одинаковые пары банков, удваивая количество необходимых модулей.

Extended Data Out RAM

В 1995 году, для Pentium систем стал доступен новый тип DRAM - расширенный вывод данных (EDO) RAM. EDO, модифицированная форма памяти FPM, иногда упоминаемая как режим Hyper Page. EDO была изобретена и запатентована компанией Micron Technology, хотя Micron лицензировала производство для многих других производителей памяти.

Память EDO состоит из специально изготовленных микросхем, которые позволяют перекрывать тайминг между последовательными доступами. Вывод расширенных данных имени указывает на то, что в отличие от FPM, драйверы вывода данных на чипе, когда контроллер памяти удаляет адрес столбца, чтобы начать следующий цикл, не отключаются. Это позволяет следующим циклом перекрывать предыдущий, экономя около 10ns за цикл.

Эффект EDO заключается в том, что уменьшается время цикла, позволяя контроллеру памяти, пока он считывает данные по текущему адресу, начинать новую инструкцию адреса столбца. Это почти идентично тому, что было достигнуто в старых системах чередованием банков памяти. Но, в отличие от чередования, с EDO устанавливать в системе одновременно два одинаковых банка памяти не нужно.

EDO RAM, по сравнению с 5-3-3-3 стандартного режима быстрой памяти, обеспечивает циклический пакетный режим 5-2-2-2. Чтобы выполнить четыре передачи памяти, EDO, по сравнению с 14 полными циклами для FPM, потребуется 11 общих системных циклов. Это 22% -ное улучшение общего времени циклов.

Результирующее двухцикличное (30ns) время цикла во время пакетных передач, по сравнению с 45 ns/22 МГц для FPM, равно 33,3 МГц эффективной тактовой частоты. В системе с 64-битной (8-байтной) шиной памяти, это приведёт к максимальной пропускной способности 266 Мбит/с (33,3 МГц × 8 байтов = 266 Мбит/с).

Из-за кэша процессора, EDO обычно повышала общую скорость тестирования системы только на 5% или меньше.

Несмотря на то, что общее улучшение системы было небольшим, существенным в EDO было то, что он использовал тот же базовый дизайн чипов DRAM, что и FPM. То есть, для FPM практически не было никаких дополнительных затрат. Фактически, в период его расцвета EDO стоила меньше, чем FPM, но предлагала более высокую производительность.

EDO RAM обычно поставлялось в 72-контактной SIMM форме.

Чтобы на самом деле использовать память EDO, ваш чипсет должен был его поддерживать. Большинство, представленных на рынке с 1995 года (Intel 430FX) до 1997 года (Intel 430TX) чипсетов для материнских плат, предполагали поддержку EDO, сделав EDO самой популярной формой памяти на ПК с 1995 по 1998 год. Поскольку чипы памяти EDO стояли столько же, как и стандартные чипы, к тому же сочетали поддержку Intel для EDO в чипсетах материнских плат, рынок ПК выбрал EDO.

EDO RAM использовалось в системах с частотой шины до 66МГц, что идеально подходило для рынка ПК до 1998 года. Однако, начиная с 1998 года, с появлением 100-мегагерцовых и более быстрых системных шин, рынок для EDO быстро упал, стандартом стала более быстрая архитектура SDRAM.

Одна вариация EDO, которая совсем не стала известной, называлась burst EDO (BEDO). BEDO добавила возможности для передачи данных даже более быстрые, чем стандартный EDO. К сожалению, технология принадлежала Micron, а не свободному отраслевому стандарту, поэтому его поддерживал только один чипсет (Intel 440FX Natoma). BEDO быстро затмилась отраслевой SDRAM, которая стала популярной среди системных чипсетов ПК и системных дизайнеров проприетарных проектов. Таким образом, BEDO действительно никогда не вышел в производство, и нет систем которые его использовали.

SDRAM

SDRAM сокращает тайминг DRAM. Тип DRAM стандарта JEDEC, работает в синхронизации с шиной памяти. SDRAM предоставляет информацию в высокоскоростных пакетах с использованием высокоскоростного синхронизированного интерфейса. Поскольку сигналы синхронизируются с часами материнской платы, SDRAM удаляет большую часть задержки асинхронной DRAM.

Как и любому новому типу памяти, прежде чем его можно будет использовать в системах, требуется поддержка чипсета на материнской плате. Начиная с 1996 года с 430VX и 430TX, большинство чипсетов Intel начали поддерживать стандартную SDRAM, а в 1998 году внедрение чипсета 440BX заставило SDRAM затмить EDO как самый популярный тип на рынке.

Производительность SDRAM, по сравнению с производительностью ОЗУ FPM или EDO, значительно улучшена. Однако, поскольку SDRAM по-прежнему тип DRAM, начальная задержка одинакова, но время цикла в пакетном режиме намного быстрее, чем при использовании FPM или EDO. Тайминг SDRAM для доступа к пакету 5-1-1-1, что означает, четыре чтения памяти будут завершены всего в восьми циклах системной шины, по сравнению с 11 циклами для EDO и 14 циклами для FPM. Это делает SDRAM почти на 20% быстрее, чем EDO.

SDRAM, кроме возможности работать меньшими циклами, способен поддерживать циклическую системную шину до 133 МГц (7,5ns). В большинстве продающихся с 1998 по 2002 год системах PC включена память SDRAM.

SDRAM продаётся в форме DIMM и обычно оценивается тактовой частотой (МГц), а не временем цикла (ns). Это во время первоначального перехода от FPM и EDO DRAM сбивало с толку.

Чтобы удовлетворить строгие требования тайминга на свои чипсеты, Intel разработала для SDRAM спецификации, под названием PC66 и PC100. Например, кажется, что для работы на частоте 100 МГц, 10ns будет достаточно, но, предлагаемая Intel спецификация PC100, потребовала более быструю память 8ns. Гарантируя этим, что все временные параметры будут удовлетворены с достаточным запасом для ошибок.

В мае 1999 года JEDEC создала спецификации под названием PC133. Увеличение скорости до 33 MHz достигается за счёт спецификации PC100, ужесточения тайминга и параметров ёмкости. Более быстрый PC133 быстро попал на все системы с 133-мегагерцовой процессорной шиной. Исходные, используемые в модулях PC133 чипы, рассчитаны на 7,5ns или 133 МГц. Более поздние чипы имели разряд в 7,0ns, что технически составляет 143МГц. Эти более быстрые чипы по-прежнему использовались на модулях PC133, но они позволяли улучшать задержку стробирования по столбцам (сокращённо CAS или CL), что несколько улучшает общее время циклирования памяти.

SDRAM обычно поставлялся с 168-контактными модулями DIMM, работающими на нескольких скоростях. В таблице ниже приведены стандартные скорости передачи данных SDRAM с одной скоростью передачи данных и, соответственно, пропускная способность.

SDRAM модуль стандарта JEDEC (168-контактный DIMM) "Скорости" и "Скорость передачи"

| Тип модуля | Тип чипа | Тактовая частота | Циклы в течение времени | Скорость шины | Ширина шины | Скорость передачи данных |

| PC66 | 15ns\10ns | 66MHz | 1 | 66MTps | 8 bytes | 533MBps |

| PC100 | 8ns | 100MHz | 1 | 100MTps | 8 bytes | 800MBps |

| PC133 | 7.5ns\7ns | 133MHz | 1 | 133MTps | 8 bytes | 1.066MBps |

МГц = миллион циклов в секунду

MTps = миллионов переводов в секунду

Мбит/с = миллион байт в секунду

NS = наносекунд (миллиардных долей секунды)

Некоторые производители продавали модули, которые, по их утверждению, были «PC150» или «PC166», хотя эти скорости не существовали как официальные стандарты JEDEC или Intel, и чипсеты или процессоры официально эти скорости не поддерживали. Эти модули фактически использовали собранные с частотой 133 МГц чипы, которые могли работать разогнанными на частотах 150 МГц или 166 МГц.

По сути, память PC150 или PC166 была памятью PC133, которая была протестирована для работы на разогнанных скоростях, не поддерживаемых оригинальным производителем чипов. Эта разгоняемая память продавалась энтузиастам, которые хотели разгонять свои чипсеты на материнской плате, тем самым увеличивая скорость процессора и шины памяти.

Внимание . В общем память PC133 считается обратно совместимой с памятью PC100. Однако некоторые чипсеты или материнские платы имели более конкретные требования для определённых типов 100 или 133 МГц чипов и конструкций модуля. Если вам необходимо обновить более старую, требующую памяти PC100 систему, но PC133 память не идентифицирована поставщиком как совместимая с вашей системой, приобретать её не стоит. Для покупки памяти, чтобы гарантировать её валентность для вашей системы, вы можете использовать предоставляемые большинством основных производителей памяти, онлайн-инструменты.

Как правило, вы обнаружите модули SDRAM с классом CL 2 или CL 3.

Страница 2 из 4

Разновидности DRAM

Синхронное выполнение

Сейчас уже не актуально использовать 66-МГц шины памяти. Разработчики DRAM нашли возможность преодолеть этот рубеж и извлекли некоторые дополнительные преимущества путем осуществления синхронного интерфейса.

С асинхронным интерфейсом процессор должен ожидать, пока DRAM закончит выполнение своих внутренних операций, которые обычно занимают около 60 нс. С синхронным управлением DRAM происходит защелкивание информации от процессора под управлением системных часов. Триггеры запоминают адреса, сигналы управления и данных, что позволяет процессору выполнять другие задачи. После определенного количества циклов данные становятся доступны, и процессор может считывать их с выходных линий.

Другое преимущество синхронного интерфейса заключается в том, что системные часы задают только временные границы, необходимые DRAM. Это исключает необходимость наличия множества стробирующих импульсов. В результате упрощается ввод, т. к. контрольные сигналы адреса данных могут быть сохранены без участия процессора и временных задержек. Подобные преимущества также реализованы и в операциях вывода.

Типы высокоскоростной памяти

Всю память с произвольным доступом (RAM) можно разделить на два типа: DRAM (динамическая RAM) и SRAM (статическая RAM).

К первому поколению высокоскоростных DRAM главным образом относят EDO DRAM, SDRAM и RDRAM, а к следующему - ESDRAM, DDR SDRAM, Direct RDRAM, SLDRAM (ранее SynchLink DRAM) и т. д.

SDRAM

SDRAM способна работать на частоте, превышающей частоту работы EDO DRAM. В первой половине 1997 г. SDRAM занимала примерно 25% всего рынка DRAM. Как и предполагалось, к 1998 г. она стала наиболее популярной из существующих высокоскоростных технологий и занимала более 50% рынка памяти. Первоначально SDRAM работала на частоте от 66 до 100 МГц. Сейчас существует память, работающая на частотах от 125 до 143 МГц и даже выше.

Модуль SDRAM на 250Мбайт.

Enhanced SDRAM (ESDRAM)

Для преодоления некоторых проблем с задержкой сигнала, присущих стандартным DRAM-модулям, производители решили встроить небольшое количество SRAM в чип, т. е. создать на чипе кэш. Одним из таких решений, заслуживающих внимания, является ESDRAM от Ramtron International Corporation.

ESDRAM - это по существу SDRAM плюс немного SRAM. При малой задержке и пакетной работе достигается частота до 200 МГц. Как и в случае внешней кэш-памяти, DRAM-кэш предназначен для хранения наиболее часто используемых данных. Следовательно, уменьшается время доступа к данным медленной DRAM.

DDR SDRAM (SDRAM II)

DDR SDRAM (Double Date Rate SDRAM) является синхронной памятью, реализующей удвоенную скорость передачи данных по сравнению с обычной SDRAM. DDR SDRAM не имеет полной совместимости с SDRAM, хотя использует метод управления, как у SDRAM, и стандартный 168-контактный разъем DIMM.

Наклейка соответствия модуля спецификации SDRAM PC100.

DDR SDRAM достигает удвоенной пропускной способности за счет работы на обеих границах тактового сигнала (на подъеме и спаде), а SDRAM работает только на одной.

SLDRAM

Стандарт SLDRAM является открытым, т. е. не требует дополнительной платы за лицензию, дающую право на производство чипов, что позволяет снизить их стоимость. Подобно предыдущей технологии, SLDRAM использует обе границы тактового сигнала. Что касается интерфейса, то SLDRAM перенимает протокол, названный SynchLink Interface. Эта память стремится работать на частоте 400 МГц.

У всех предыдущих DRAM были разделены линии адреса, данных и управления, которые накладывают ограничения на скорость работы устройств. Для преодоления этого ограничения в некоторых технологических решениях все сигналы стали выполняться на одной шине. Двумя из таких решений являются технологии SLDRAM и DRDRAM. Они получили наибольшую популярность и заслуживают внимания.

Модуль памяти DRDRAM.

RDRAM (Rambus DRAM)

RDRAM представляет спецификацию, созданную Rambus, Inc. Частота работы памяти равна 400 МГц, но за счет использования обеих границ сигнала достигается частота, эквивалентная 800 МГц. Спецификация Rambus сейчас наиболее интересна, так что остановимся на ней подробнее.

Модули от Rambus, Inc.

Direct Rambus™ DRAM - это высокоскоростная динамическая память с произвольным доступом, разработанная Rambus, Inc. Она обеспечивает высокую пропускную способность по сравнению с большинством других DRAM. Direct Rambus DRAMs представляет интегрированную на системном уровне технологию.

Работа Direct RDRAMtm определяется требованиями подсистемы Direct Rambus. Для понимания деталей спецификации Direct Rambus DRAM необходимо понять подсистему памяти Rambus™ в целом.

Direct Rambus Memory System

Подсистема памяти Direct Rambus включает следующие компоненты:

- Direct Rambus Controller

- Direct Rambus Channel

- Direct Rambus Connector

- Direct Rambus RIMM(tm)

- Direct Rambus DRAMs

Физические, электрические и логические части всех этих компонентов определены и специфицированы Rambus, Inc. Это требуется для совместимости и высокоскоростной работы подсистемы Direct Rambus.

Direct Rambus Controller

Контроллер Direct Rambus - это главная шина подсистемы памяти. Он помещается на чипе логики, таком, как PC-чипсет, микропроцессор, графический контроллер или ASIC. Физически можно поместить до четырех Direct Rambus-контроллеров на одном чипе логики. Контроллер представляет собой интерфейс между чипом логики и каналом Direct Rambus. В его обязанности входит генерирование запросов, управление потоком данных и еще ряд функций.

Direct Rambus-контроллер состоит из двух самостоятельных блоков: Rambus ASIC Cell (RAC) и Rambus Memory Controller (RMC).

Direct Rambus Channel

Direct Rambus Channel создает электрическое соединение между Rambus-контроллером и чипами Direct RDRAM. Работа канала основана на 30-ти сигналах, составляющих высокоскоростную шину. Эта шина работает на тактовой частоте 400 МГц и позволяет передавать данные на 800 МГц (данные передаются на обеих границах такта). Такая высокая частота достигается за счет использования некоторых технических приемов. Два канала данных (шириной в байт каждый) позволяют получить пиковую пропускную способность в 1,6 Гбайт/с.

Канал может быть выполнен на обычных системных платах и соответствует форм-фактору SDRAM.

Direct Rambus Connector

Разъем Direct Rambus представляет низкоиндуктивный интерфейс между каналом на модуле RIMM и каналом на материнской плате. Connector - разъем со 168 контактами. Контакты размещены на двух сторонах модуля по 84 с каждой стороны.

Direct Rambus RIMM

Direct Rambus RIMM - это модуль памяти, который включает один или более Direct RDRAM-чипов и организует непрерывность канала. Канал входит в модуль на одном конце, проходит через все чипы DRAM и выходит на другом. По существу RIMM образует непрерывный канал на пути от одного разъема к другому. Недопустимо оставлять свободными разъемы, потому что это приведет к разрыву канала с терминатором, находящимся на системной плате в конце канала. Для решения этой проблемы разработаны модули только с каналом (чипы памяти отсутствуют). Они называются continuity modules и предназначены для заполнения свободных посадочных мест.

Модули Direct Rambus имеют геометрические размеры, сходные с размерами SDRAM DIMMs. Это позволяет вставлять RIMM"ы во все материнские платы с соответствующим форм-фактором. Модули имеют 168 контактов. Еще модули RIMM поддерживают SPD, который используется на DIMM"ах SDRAM. В отличие от SDRAM DIMM, Direct Rambus может содержать любое целое число чипов Direct RDRAM (до максимально возможного).

Direct Rambus RIMMs могут быть как односторонние, так и двухсторонние. Односторонние RIMM используют шестислойную плату и могут содержать от одного до восьми чипов Direct RDRAM. Двухсторонние RIMM используют восьмислойную плату и могут содержать до 16-ти чипов Direct DRAM. Для гарантии совместимости различных товаров Rambus, Inc. обеспечивает некоторые правила конструирования.

Memory Expansion

Один канал Direct Rambus максимум может поддерживать 32 чипа Direct RDRAM. В материнской плате может использоваться до трех RIMM-модулей. Используя 64-Мбит, 128-Мбит и 256-Мбит устройства, максимальная емкость памяти на канал достигает 256 Мбайт, 512 Мбайт и 1Гбайт соответственно. Для поддержки целостности канала все свободные RIMM-слоты должны заполняться continuity-модулями.

Чтобы расширить канал сверх 32 устройств, могут использоваться два чипа повторителя. С одним повторителем канал может поддерживать 64 устройства на 6 RIMM-модулях, а с двумя - 128 устройств на 12.

Direct Rambus DRAM

Чипы Direct Rambus DRAM составляют часть подсистемы Rambus, запоминающую данные. Все устройства в системе электрически расположены на канале между контроллером и терминатором. Устройства Direct Rambus могут только отвечать на запросы контроллера, который делает их шину подчиненной или отвечающей. Устройства можно разделить на две части.

Технология Direct Rambus представляет собой третий этап развития памяти RDRAM. Впервые память RDRAM появилась в 1995 г., работала на частоте 150 МГц и обеспечивала пропускную способность 600 Мбайт/с. Она использовалась в станциях SGI Indigo2 IMPACTtm, в приставках Nintendo64, а также в качестве видеопамяти. Следующее поколение RDRAM появилось в 1997 г. под названием Concurrent RDRAM. Новые модули были полностью совместимы с первыми. Но за год до этого события в жизни компании произошло не менее значимое событие. В декабре 1996 г. Rambus, Inc. и Intel Corporation объявили о совместном развитии памяти RDRAM и продвижении ее на рынок персональных компьютеров.

Лекция №4 Система памяти

План:

Введение

1. Классификация типов памяти.

2. Память ROM, SRAM, DRAM.

Введение

Память – это свойство, которым обладает живое существо или устройство.

Компьютерная память (устройство хранения информации, запоминающее устройство) - часть вычислительной машины, физическое устройство или среда для хранения данных, используемых в вычислениях, в течение определённого времени.

В персональных компьютерах «памятью» часто называют один из её видов - динамическая память с произвольным доступом (DRAM), - которая в настоящее время используется в качестве ОЗУ персонального компьютера.

Работоспособность всей компьютерной системы зависит не только от оперативной памяти, но и от подсистемы памяти в целом.

Подсистема памяти охватывает:

оперативную память;

кэш-память процессора;

контроллер памяти;

шины данных и команд.

Рост требуемых объемов оперативной (системной) памяти происходит практически непрерывно по мере развития технологии аппаратных средств и программных продуктов. Сегодня повсеместным стандартом для оперативной памяти становится объем 4 ГБ.

1. Классификация типов памяти

Следует различать классификацию памяти и классификацию запоминающих устройств (ЗУ). Первая классифицирует память по функциональности, вторая же - по технической реализации. Здесь рассматривается первая - таким образом, в неё попадают как аппаратные виды памяти (реализуемые на ЗУ), так и структуры данных, реализуемые в большинстве случаев программно.

Доступные операции над данными в памяти

Память только для чтения (read-only memory, ROM)

Память для чтения/записи

Память на программируемых и перепрограммируемых ПЗУ (ППЗУ и ПППЗУ) не имеет общепринятого места в этой классификации. Её относят либо к подвиду памяти «только для чтения», либо выделяют в отдельный вид.

Также предлагается относить память к тому или иному виду по характерной частоте её перезаписи на практике: к RAM относить виды, в которых информация часто меняется в процессе работы, а к ROM - предназначенные для хранения относительно неизменных данных.

Энергозависимость

Энергонезависимая память (англ. nonvolatile storage) - память, реализованная ЗУ, записи в которых не стираются при снятии электропитания. К этому типу памяти относятся все виды памяти на ПЗУ и ППЗУ;

Энергозависимая память (англ. volatile storage) - память, реализованная ЗУ, записи в которых стираются при снятии электропитания. К этому типу памяти относятся память на ОЗУ, кэш-память.

— Статическая память (англ. static storage) - энергозависимая память, которой для хранения информации достаточно сохранения питающего напряжения;

— Динамическая память (англ. dynamic storage) - энергозависимая памяти, в которой информация со временем разрушается (деградирует), и, кроме подачи электропитания, необходимо производить её периодическое восстановление (регенерацию).

Метод доступа

Последовательный доступ (англ. sequential access memory, SAM) - ячейки памяти выбираются (считываются) последовательно, одна за другой, в очерёдности их расположения. Вариант такой памяти - стековая память.

Произвольный доступ (англ. random access memory, RAM) - вычислительное устройство может обратиться к произвольной ячейке памяти по любому адресу.

Назначение

Буферная память (англ. buffer storage) - память, предназначенная для временного хранения данных при обмене ими между различными устройствами или программами.

Временная (промежуточная) память (англ. temporary (intermediate) storage) - память для хранения промежуточных результатов обработки.

Кеш-память (англ. cache memory) - часть архитектуры устройства или программного обеспечения, осуществляющая хранение часто используемых данных для предоставления их в более быстрый доступ, нежели кешируемая память.

Корректирующая память (англ. patch memory) - часть памяти ЭВМ, предназначенная для хранения адресов неисправных ячеек основной памяти. Также используются термины «relocation table» и «remap table».

Управляющая память (англ. control storage) - память, содержащая управляющие программы или микропрограммы. Обычно реализуется в виде ПЗУ.

Разделяемая память или память коллективного доступа (англ. shared memory, shared access memory) - память, доступная одновременно нескольким пользователям, процессам или процессорам.

Организация адресного пространства

Реальная или физическая память (англ. real (physical) memory) - память, способ адресации которой соответствует физическому расположению её данных;

Виртуальная память (англ. virtual memory) - память, способ адресации которой не отражает физического расположения её данных;

Оверлейная память (англ. overlayable storage) - память, в которой присутствует несколько областей с одинаковыми адресами, из которых в каждый момент доступна только одна.

Удалённость и доступность для процессора

Первичная память доступна процессору без какого-либо обращения к внешним устройствам. Это регистры процессора(процессорная или регистровая память) и кэш процессора (если есть);

Вторичная память доступна процессору путём прямой адресацией через шину адреса (Адресуемая память) или через другие выводы. Таким образом доступна основная память (память, предназначенная для хранения текущих данных и выполняемых программ) и порты ввода-вывода (специальные адреса, через обращение к которым реализовано взаимодействие с прочей аппаратурой);

Третичная память доступна только путём нетривиальной последовательности действий. Сюда входят все виды внешней памяти - доступной через устройства ввода-вывода. Взаимодействие с третичной памятью ведётся по определённым правилам (протоколам) и требует присутствия в памяти соответствующих программ. Программы, обеспечивающие минимально необходимое взаимодействие, помещаются в ПЗУ, входящее во вторичную память (у PC-совместимых ПК - это ПЗУ BIOS);

Положение структур данных, расположенных в основной памяти, в этой классификации неоднозначно. Как правило, их вообще в неё не включают, выполняя классификацию с привязкой к традиционно используемым видам ЗУ.

Управление процессором

Непосредственно управляемая (оперативно доступная) память (англ. on-line storage) - память, непосредственно доступная в данный момент времени центральному процессору.

Автономная память.

Организация хранения данных и алгоритмы доступа к ним

Повторяет классификацию структур данных.

Адресуемая память - адресация осуществляется по местоположению данных.

Ассоциативная память (англ. associative memory, content-addressable memory, CAM) - адресация осуществляется по содержанию данных, а не по их местоположению.

Магазинная (стековая) память (англ. pushdown storage) - реализация стека.

Матричная память (англ. matrix storage) - ячейки памяти расположены так, что доступ к ним осуществляется по двум или более координатам.

Объектная память (англ. object storage) - память, система управления которой ориентирована на хранение объектов. При этом каждый объект характеризуется типом и размером записи.

Семантическая память (англ. semantic storage) - данные размещаются и списываются в

Физические принципы

Эта классификация повторяет соответствующую классификацию ЗУ.

Разновидности магнитной памяти

Память на магнитной ленте (англ. magnetic tape memory) - представляет собой пластиковую узкую ленту с магнитным покрытием и механизм с блоком головок записи-воспроизведения (БГЗВ). Лента намотана на бобину, и последовательно протягивается лентопротяжным механизмом (ЛПМ) возле БГЗВ. Запись производится перемагничиванием частиц магнитного слоя ленты при прохождении их возле зазора головки записи. Считывание записанной информации происходит при прохождении намагниченного ранее участка плёнки возле зазора головки воспроизведения.

Память на магнитных дисках (англ. magnetic disk memory) - представляет собой круглый пластиковый диск с магнитным покрытием и механизм с БГЗВ. Данные при этом наносятся радиально, при вращении диска вокруг своей оси и радиальном сдвиге БГЗВ на шаг головки. Запись производится перемагничиванием частиц магнитного слоя диска при прохождении их возле зазора головки записи. Считывание записанной информации происходит при прохождении намагниченного ранее участка возле зазора головки воспроизведения.

Память на магнитной проволоке (англ. plated wire memory) Использовалась в магнитофонах до магнитной ленты. В настоящее время по этому принципу конструируется большинство авиационных т. н. «чёрных ящиков» - данный носитель имеет наиболее высокую устойчивость к внешним воздействиям и высокую сохранность даже при повреждениях в аварийных ситуациях.

Ферритовая память (англ. core storage) - ячейка представляет собой ферритовый сердечник, изменение состояния которого (перемагничивание) происходит при пропускании тока через намотанный на него проводник. В настоящее имеет ограниченное применение, в основном в военной сфере.

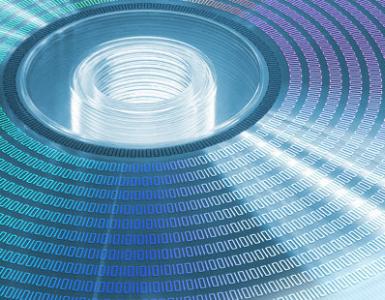

Разновидности оптической памяти

Фазоинверсная память (англ. Phase Change Rewritable storage, PCR) - оптическая память, в которой рабочий (отражающий) слой выполнен из полимерного вещества, способного при нагреве менять фазовое состояние (кристаллическое↔аморфное) и отражающие характеристики в зависимости от режима нагрева. Применяется в перезаписываемых оптических дисках (CD-RW, DVD-RW).

2. Память ROM, SRAM, DRAM.

В современных компьютерах используются запоминающие устройства трех основных типов:

ROM (Read Only Memory). Постоянное запоминающее устройство — ПЗУ, неспособное выполнять операцию записи данных.

DRAM (Dynamic Random Access Memory). Динамическое запоминающее устройство с произвольным порядком выборки.

SRAM (Static RAM). Статическая оперативная память.

Память типа ROM

В памяти типа ROM (Read Only Memory), или ПЗУ (постоянное запоминающее устройство), данные можно только хранить, изменять их нельзя. Именно поэтому такая память используется только для чтения данных. ROM также часто называется энергонезависимой памятью, потому что любые данные, записанные в нее, сохраняются при выключении питания. Поэтому в ROM помещаются команды запуска ПК, т.е. программное обеспечение, которое загружает систему.

Рисунок ROM-память

Рисунок ROM-память

ROM и оперативная память — не противоположные понятия. На самом деле ROM представляет собой часть оперативной памяти системы. Другими словами, часть адресного пространства оперативной памяти отводится для ROM. Это необходимо для хранения программного обеспечения, которое позволяет загрузить операционную систему.

Основной код BIOS содержится в микросхеме ROM на системной плате, но на платах адаптеров также имеются аналогичные микросхемы. Они содержат вспомогательные подпрограммы BIOS и драйверы, необходимые для конкретной платы, особенно для тех плат, которые должны быть активизированы на раннем этапе начальной загрузки, например видеоадаптер. Платы, не нуждающиеся в драйверах на раннем этапе начальной загрузки, обычно не имеют ROM, потому что их драйверы могут быть загружены с жесткого диска позже — в процессе начальной загрузки. Рисунок ROM-память

Рисунок ROM-память

В настоящее время в большинстве систем используется одна из форм Flash-памяти, которая называется электрически стираемой программируемой постоянной памятью (Electrically Erasable Programmable Readonly Memory — EEPROM). Flash-память является по-настоящему энергонезависимой и перезаписываемой, она позволяет пользователям легко модифицировать ROM, программно-аппаратные средства системных плат и других компонентов (таких, как видеоадаптеры, платы SCSI, периферийные устройства и т.п.).

SRAM(кэш-память)

Существует тип памяти, совершенно отличный от других, — статическая оперативная память (Static RAM — SRAM). Она названа так потому, что, в отличие от динамической оперативной памяти (DRAM), для сохранения ее содержимого не требуется периодической регенерации. Это не единственное ее преимущество. SRAM имеет более высокое быстродействие, чем DRAM, и может работать на той же частоте, что и современные процессоры.

Статическая память — это тип памяти, в котором значение бита информация хранится в ячейке определяющаяся наличием или отсутствием заряда на миниатюрном конденсаторе (управляемом транзисторами).

В статической памяти применяются специальные элементы — триггеры, реализованные на 4-6 транзисторах. Именно триггер является ячейкой статической памяти.

Рисунок Схема ячейки статической памяти

Транзистор – трехэлектродный полупроводниковый прибор для усиления, генерирования и преобразования электрических колебаний, выполненный на основе монокристаллического полупроводника.

Триггер — логический элемент с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Такое устройство сохраняет свое состояние, до тех пор, пока подается питание. Время срабатывания триггера составляет в современных микросхемах не более 2нс (Pentium 4 3,6 GHz = 0.28нс; Athlon XP 2,2GHz = 0.41нс). SRAM различается по принципу работы.

Существует три типа:

1. Async SRAM (Asynchronous Static Random Access Memory) — асинхронная статическая память с произвольным порядком выборки;

2. SyncBurst SRAM (Synchronous Burst Random Access Memory) – синхронная пакетная статическая память с произвольным порядком выборки;

3. PipBurst SRAM (Pipelined Burst Random Access Memory) – конвейерная пакетная статическая память с произвольным порядком выборки;

Async SRAM

– это устаревший тип памяти, асинхронный интерфейс которой схож с интерфейсом DRAM и включает в себя шины адреса, данных и управления.

SyncBurst SRAM

– этот тип памяти синхронизирован с системной шиной и лучше всего подходит для выполнения пакетных операций. Ну а интерфейс PipBurst SRAM схож с интерфейсом SyncBurst SRAM, но позволяет получать данные без тактов ожидания.

Как правило, чем больше объем кэш, тем система производительней. Но сам по себе объем еще не гарантирует высокой производительности. Для кэш главное – контроллер.

Время доступа SRAM 2 нс. означает, что такая память может работать синхронно с процессорами на частоте 500 МГц или выше. Однако для хранения каждого бита в конструкции SRAM используется кластер из шести транзисторов. Использование транзисторов без каких либо конденсаторов означает, что нет необходимости в регенерации. (Ведь если нет никаких конденсаторов, то и заряды не теряются.) Пока подается питание, SRAM будет помнить то, что сохранено.

По сравнению с DRAM быстродействие SRAM намного выше, но плотность ее гораздо ниже, а цена довольно высока. Более низкая плотность означает, что микросхемы SRAM имеют большие габариты, хотя их информационная емкость намного меньше. Большое число транзисторов и кластеризованное их размещение не только увеличивает габариты микросхем SRAM, но и значительно повышает стоимость технологического процесса по сравнению с аналогичными параметрами для микросхем DRAM. Например, емкость модуля DRAM может равняться 64 Мбайт или больше, в то время как емкость модуля SRAM приблизительно того же размера составляет только 2 Мбайт, причем их стоимость будет одинаковой. Таким образом, габариты SRAM в среднем в 30 раз превышают размер DRAM, то же самое можно сказать и о стоимости. Все это не позволяет использовать память типа SRAM в качестве оперативной памяти в персональных компьютерах.

Память типа DRAM

DRAM (Dynamic Random Access Memory) - тип энергозависимой полупроводниковой памяти с произвольным доступом (RAM), также запоминающее устройство, наиболее широко используемое в качестве ОЗУ современных компьютеров.

Физически память DRAM состоит из ячеек, созданных в полупроводниковом материале, в каждой из которых можно хранить определённый объём данных, от 1 до 4 бит. Совокупность ячеек такой памяти образуют условный «прямоугольник», состоящий из определённого количества строк и столбцов. Один такой «прямоугольник» называется страницей, а совокупность страниц называется банком. Весь набор ячеек условно делится на несколько областей.

Рисунок Схема ячейки динамической памяти

Рисунок Схема ячейки динамической памяти

Основное преимущество памяти этого типа состоит в том, что ее ячейки упакованы очень плотно, т.е. в небольшую микросхему можно упаковать много битов, а значит, на их основе можно построить память большой емкости.

Ячейки памяти в микросхеме DRAM — это крошечные конденсаторы, которые удерживают заряды. Именно так (наличием или отсутствием зарядов) и кодируются биты. Проблемы, связанные с памятью этого типа, вызваны тем, что она динамическая, т.е. должна постоянно регенерироваться, так как в противном случае электрические заряды в конденсаторах памяти будут “стекать” и данные будут потеряны. Регенерация происходит, когда контроллер памяти системы берет крошечный перерыв и обращается ко всем строкам данных в микросхемах памяти. Большинство систем имеют контроллер памяти (обычно встраиваемый в набор микросхем системной платы), который настроен на соответствующую промышленным стандартам частоту регенерации, равную, например, 15 мкс. Ко всем строкам данных обращение осуществляется по прохождении 128 специальных циклов регенерации. Это означает, что каждые 1,92 мс (128×15 мкс) прочитываются все строки в памяти для обеспечения регенерации данных.

Регенерация памяти, к сожалению, отнимает время у процессора: каждый цикл регенерации по длительности занимает несколько циклов центрального процессора. В старых компьютерах циклы регенерации могли занимать до 10% (или больше) процессорного времени, но в современных системах, работающих на частотах, равных сотням мегагерц, расходы на регенерацию составляют 1% (или меньше) процессорного времени. Некоторые системы позволяют изменить параметры регенерации с помощью программы установки параметров CMOS, но увеличение времени между циклами регенерации может привести к тому, что в некоторыхячейках памяти заряд “стечет”, а это вызовет сбои памяти. В большинстве случаев надежнее придерживаться рекомендуемой или заданной по умолчанию частоты регенерации. Поскольку затраты на регенерацию в современных компьютерах составляют менее 1%, изменение частоты регенерации оказывает незначительное влияние на характеристики компьютера. Одним из наиболее приемлемых вариантов является использование для синхронизации памяти значений по умолчанию или автоматических настроек, заданных с помощью Setup BIOS. Большинство современных систем не позволяют изменять заданную синхронизацию памяти, постоянно используя автоматически установленные параметры. При автоматической установке системная плата считывает параметры синхронизации из системы определения последовательности в ПЗУ (serial presence detect — SPD) и устанавливает частоту периодической подачи импульсов в соответствии с полученными данными.

В устройствах DRAM для хранения одного бита используется только один транзистор и пара конденсаторов, поэтому они более вместительны, чем микросхемы других типов памяти. В настоящее время имеются микросхемы динамической оперативной памяти емкостью 4Гбайт и больше. Это означает, что подобные микросхемы содержат более миллиарда транзисторов. В микросхеме памяти все транзисторы и конденсаторы размещаются последователь но, обычно в узлах квадратной решетки, в виде очень простых, периодически повторяющихся структур.

Транзистор для каждого одноразрядного регистра DRAM используется для чтения состояния смежного конденсатора. Если конденсатор заряжен, в ячейке записана 1; если заряда нет — записан 0. Заряды в крошечных конденсаторах все время стекают, вот почему память должна постоянно регенерироваться. Даже мгновенное прерывание подачи питания или какой-нибудь сбой в циклах регенерации приведет к потере заряда в ячейке DRAM, а следовательно, и к потере данных. В работающей системе подобное приводит к появлению “синего” экрана, глобальным отказам системы защиты, повреждению файлов или к полному отказу системы.

Динамическая оперативная память используется в персональных компьютерах; поскольку она недорогая, микросхемы могут быть плотно упакованы, а это означает, что запоминающее устройство большой емкости может занимать небольшое пространство. К сожалению, память этого типа не отличается высоким быстродействием, обычно она намного “медленнее” процессора. Поэтому существует множество различных типов организации DRAM, позволяющих улучшить эту характеристику.

Характеристики памяти DRAM

Основными характеристиками DRAM являются рабочая частота и тайминги.

При обращении к ячейке памяти контроллер памяти задаёт номер банка, номер страницы в нём, номер строки и номер столбца и на все эти запросы тратится время, помимо этого довольно большой период уходит на открытие и закрытие банка после самой операции. На каждое действие требуется время, называемое таймингом.

Основными таймингами DRAM являются:

- задержка между подачей номера строки и номера столбца, называемая временем полного доступа (англ. RAS to CAS delay), з

- адержка между подачей номера столбца и получением содержимого ячейки, называемая временем рабочего цикла (англ. CAS delay),

- задержка между чтением последней ячейки и подачей номера новой строки (англ. RAS precharge).

Тайминги измеряются в наносекундах, и чем меньше величина этих таймингов, тем быстрее работает оперативная память.

Типы DRAM:

На протяжении долгого времени разработчиками создавались различные типы памяти. Они обладали разными характеристиками, в них были использованы разные технические решения. Основной движущей силой развития памяти было развитие компьютеров и центральных процессоров. Постоянно требовалось увеличение быстродействия и объёма оперативной памяти.

Страничная память

Страничная память (англ. page mode DRAM, PM DRAM) являлась одним из первых типов выпускаемой компьютерной оперативной памяти. Память такого типа выпускалась в начале 1990-х годов, но с ростом производительности процессоров и ресурсоёмкости приложений требовалось увеличивать не только объём памяти, но и скорость её работы.

Быстрая страничная память

Быстрая страничная память (англ. fast page mode DRAM, FPM DRAM) появилась в 1995 году. Принципиально новых изменений память не претерпела, а увеличение скорости работы достигалось путём повышенной нагрузки на аппаратную часть памяти. Данный тип памяти в основном применялся для компьютеров с процессорами Intel 80486 или аналогичных процессоров других фирм. Память могла работать на частотах 25 и 33 МГц с временем полного доступа 70 и 60 нс и с временем рабочего цикла 40 и 35 нс соответственно.

3. Модули оперативной памяти SDRAM, DDR SDRAM, DDR2 SDRAM, DDR3 SDRAM и др.

EDO DRAM - память с усовершенствованным выходом

C появлением процессоров Intel Pentium память FPM DRAM оказалась совершенно неэффективной. Поэтому следующим шагом стала память с усовершенствованным выходом (англ. extended data out DRAM, EDO DRAM). Эта память появилась на рынке в 1996 году и стала активно использоваться на компьютерах с процессорами Intel Pentium и выше. Её производительность оказалась на 10-15 % выше по сравнению с памятью типа FPM DRAM. Её рабочая частота была 40 и 50 МГц, соответственно, время полного доступа - 60 и 50 нс, а время рабочего цикла - 25 и 20 нс. Эта память содержит регистр-защелку (англ. data latch) выходных данных, что обеспечивает некоторую конвейеризацию работы для повышения производительности при чтении.

SDRAM - синхронная DRAM

В связи с выпуском новых процессоров и постепенным увеличением частоты системной шины, стабильность работы памяти типа EDO DRAM стала заметно падать. Ей на смену пришла синхронная память (англ. synchronous DRAM, SDRAM). Новыми особенностями этого типа памяти являлись использование тактового генератора для синхронизации всех сигналов и использование конвейерной обработки информации. Также память надёжно работала на более высоких частотах системной шины (100 МГц и выше).

Рисунок Модуль памяти SD RAM

Рисунок Модуль памяти SD RAM

Если для FPM и EDO памяти указывается время чтения первой ячейки в цепочке (время доступа), то для SDRAM указывается время считывания последующих ячеек. Цепочка - несколько последовательных ячеек. На считывание первой ячейки уходит довольно много времени (60-70 нс) независимо от типа памяти, а вот время чтения последующих сильно зависит от типа. Рабочие частоты этого типа памяти могли равняться 66, 100 или 133 МГц, время полного доступа - 40 и 30 нс, а время рабочего цикла - 10 и 7,5 нс.

С этим типом памяти применялась технология Virtual Channel Memory (VCM). VCM использует архитектуру виртуального канала, позволяющую более гибко и эффективно передавать данные с использованием каналов регистра на чипе. Данная архитектура интегрирована в SDRAM. VCM, помимо высокой скорости передачи данных, была совместима с существующими SDRAM, что позволяло делать апгрейд системы без значительных затрат и модификаций. Это решение нашло поддержку у некоторых производителей чипсетов.

Enhanced SDRAM (ESDRAM)

Для преодоления некоторых проблем с задержкой сигнала, присущих стандартной DRAM-памяти, было решено встроить небольшое количество SRAM в чип, то есть создать на чипе кеш.

- это, по существу, SDRAM с небольшим количеством SRAM. При малой задержке и пакетной работе достигается частота до 200 МГц. Как и в случае внешней кеш-памяти, SRAM-кеш предназначен для хранения и выборки наиболее часто используемых данных. Отсюда и уменьшение времени доступа к данным медленной DRAM.

Одним из таких решений являлась ESDRAM от Ramtron International Corporation.

Рисунок Модули ESDRAM

Рисунок Модули ESDRAM

Пакетная EDO RAM

Пакетная память EDO RAM (англ. burst extended data output DRAM, BEDO DRAM) стала дешёвой альтернативой памяти типа SDRAM. Основанная на памяти EDO DRAM, её ключевой особенностью являлась технология поблочного чтения данных (блок данных читался за один такт), что сделало её работу быстрее, чем у памяти типа SDRAM. Однако невозможность работать на частоте системной шины более 66 МГц не позволила данному типу памяти стать популярным.

Рисунок Модуль EDORAM

Рисунок Модуль EDORAM

Video RAM

Специальный тип оперативной памяти - Video RAM (VRAM) - был разработан на основе памяти типа SDRAM для использования в видеоплатах. Он позволял обеспечить непрерывный поток данных в процессе обновления изображения, что было необходимо для реализации изображений высокого качества. На основе памяти типа VRAM, появилась спецификация памяти типа Windows RAM (WRAM), иногда её ошибочно связывают с операционными системами семейства Windows. Её производительность стала на 25 % выше, чем у оригинальной памяти типа SDRAM, благодаря некоторым техническим изменениям.

Рисунок Микросхема

Video RAM

Рисунок Микросхема

Video RAM

DDR SDRAM

По сравнению с обычной памятью типа SDRAM, в памяти SDRAM с удвоенной скоростью передачи данных (англ. double data rate SDRAM, DDR SDRAM или SDRAM II) была вдвое увеличена пропускная способность. Первоначально память такого типа применялась в видеоплатах, но позднее появилась поддержка DDR SDRAM со стороны чипсетов.

У всех предыдущих DRAM были разделены линии адреса, данных и управления, которые накладывают ограничения на скорость работы устройств. Для преодоления этого ограничения в некоторых технологических решениях все сигналы стали выполняться на одной шине. Двумя из таких решений являются технологии DRDRAM и SLDRAM. Они получили наибольшую популярность и заслуживают внимания. Стандарт SLDRAM является открытым и, подобно предыдущей технологии, SLDRAM использует оба перепада тактового сигнала. Что касается интерфейса, то SLDRAM перенимает протокол, названный SynchLink Interface и стремится работать на частоте 400 МГц.

Рисунок Модуль DDR SDRAM

Рисунок Модуль DDR SDRAM

Память DDR SDRAM работает на частотах в 100, 133, 166 и 200 МГц, её время полного доступа - 30 и 22,5 нс, а время рабочего цикла - 5, 3,75, 3 и 2,5 нс.

Так как частота синхронизации лежит в пределах от 100 до 200 МГц, а данные передаются по 2 бита на один синхроимпульс, как по фронту, так и по срезу тактового импульса, то эффективная частота передачи данных лежит в пределах от 200 до 400 МГц. Такие модули памяти обозначаются DDR200, DDR266, DDR333, DDR400.

Direct RDRAM или Direct Rambus DRAM

Тип памяти RDRAM является разработкой компании Rambus. Высокое быстродействие этой памяти достигается рядом особенностей, не встречающихся в других типах памяти. Первоначальная очень высокая стоимость памяти RDRAM привела к тому, что производители мощных компьютеров предпочли менее производительную, зато более дешёвую память DDR SDRAM. Рабочие частоты памяти - 400, 600 и 800 МГц, время полного доступа - до 30 нс, время рабочего цикла - до 2,5 нс.

Рисунок Модули RD RAM

Рисунок Модули RD RAM

DDR2 SDRAM

Конструктивно новый тип оперативной памяти DDR2 SDRAM был выпущен в 2004 году. Основываясь на технологии DDR SDRAM, этот тип памяти за счёт технических изменений показывает более высокое быстродействие и предназначен для использования на современных компьютерах. Память может работать с тактовой частотой шины 200, 266, 333, 337, 400, 533, 575 и 600 МГц. При этом эффективная частота передачи данных соответственно будет 400, 533, 667, 675, 800, 1066, 1150 и 1200 МГц. Некоторые производители модулей памяти помимо стандартных частот выпускают и образцы, работающие на нестандартных (промежуточных) частотах. Они предназначены для использования в разогнанных системах, где требуется запас по частоте. Время полного доступа - 25, 11,25, 9, 7,5 нс и менее. Время рабочего цикла - от 5 до 1,67 нс.

Рисунок Модуль DDR2 SDRAM

Рисунок Модуль DDR2 SDRAM

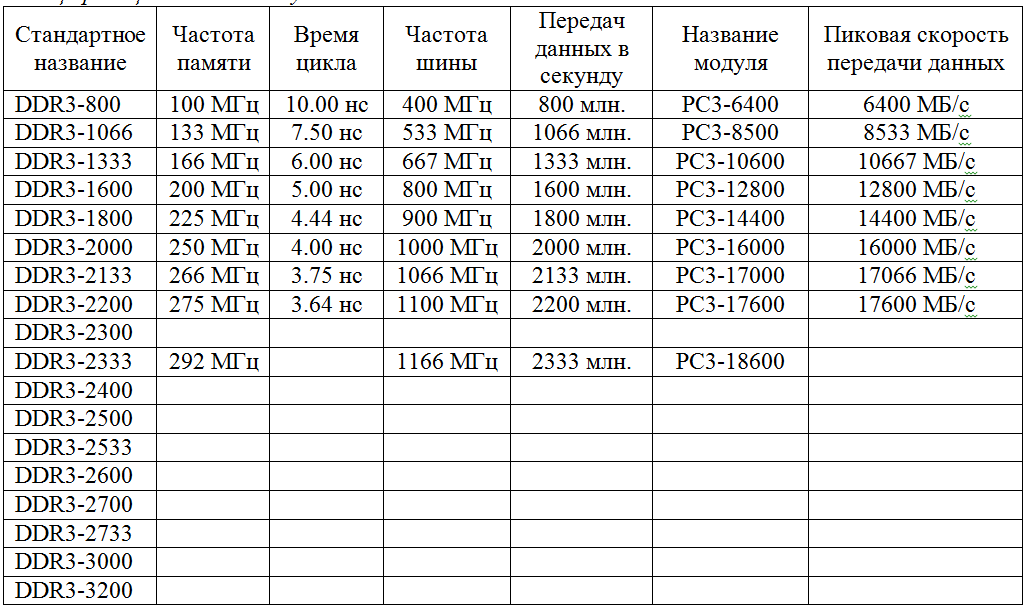

DDR3 SDRAM

Этот тип памяти основан на технологиях DDR2 SDRAM со вдвое увеличенной частотой передачи данных по шине памяти. Отличается пониженным энергопотреблением по сравнению с предшественниками. Частота полосы пропускания лежит в пределах от 800 до 2400 МГц (рекорд частоты - более 3000 МГц), что обеспечивает большую пропускную способность по сравнению со всеми предшественниками.

Рисунок Модуль DDR3 SDRAM

Рисунок Модуль DDR3 SDRAM

Конструктивные исполнения памяти DRAM

Память типа DRAM конструктивно выполняют и в виде отдельных микросхем в корпусах типа DIP, SOIC, BGA, и в виде модулей памяти типа: SIPP, SIMM, DIMM, RIMM.

Первоначально микросхемы памяти выпускались в корпусах типа DIP (к примеру, серия К565РУхх), далее они стали производится в более технологичных для применения в модулях корпусах.

На многих модулях SIMM и подавляющем числе DIMM устанавливалась SPD (Serial Presence Detect) - небольшая микросхема памяти EEPROM, хранящяя параметры модуля (ёмкость, тип, рабочее напряжение, число банков, время доступа и т. п.), которые программно были доступны как оборудованию, в котором модуль был установлен (применялось для автонастройки параметров), так и пользователям и производителям.

Модули SIPP

Модули типа SIPP (Single In-line Pin Package) представляют собой прямоугольные платы с контактами в виде ряда маленьких штырьков. Этот тип конструктивного исполнения уже практически не используется, так как он далее был вытеснен модулями типа SIMM.

Модули SIMM

Модули типа SIMM (Single In-line Memory Module) представляют собой длинные прямоугольные платы с рядом контактных площадок вдоль одной из её сторон. Модули фиксируются в разъёме (сокете) подключения с помощью защёлок, путём установки платы под некоторым углом и нажатия на неё до приведения в вертикальное положение. Имели несколько модификаций, среди которых наибольшее распространение получили три.

Первая - 30-контактный модуль, имевший объем от 256 КБайт до 16 МБайт и восьмиразрядную шину данных, дополняемую (иногда) девятой линией контроля четности памяти. Применялся в 286, 386 машинах. В случае процессоров 286, 386SX модули ставились парами, на 386DX - по четыре штуки одинаковой емкости.

30-контактный модуль SIMM.

С приходом 486 машин, для которых эти модули надо было бы ставить по четыре (как минимум) штуки был вытеснен 72-контактным модулем SIMM, который, по существу, объединил на себе 4 30-контактных модуля с общими линиями адреса и раздельными линиями данных. Таким образом, модуль становится 32-разрядным и достаточно всего одного модуля. Объем от 1 МБайт до 128 МБайт.

Характеристики:

Разрядность шины данных: 8 бит (9 бит у модулей с контролем четности)

Тип применяемых микросхем динамической памяти: FPM

Стандартные значения объема памяти модулей: 256 Кб, 1 Мб, 4 Мб, 16 Мб

Шаг расположения контактных площадок - 0,1″

Таким образом модули выпускались на 4, 8, 16, 32, 64, 128 Мбайт. Наиболее распространены 30- и 72-контактные модули SIMM.

Модули DIMM

Модули типа DIMM (Dual In-line Memory Module) представляют собой длинные прямоугольные платы с рядами контактных площадок вдоль обеих её сторон, устанавливаемые в разъём подключения вертикально и фиксируемые по обоим торцам защёлками. Микросхемы памяти на них могут быть размещены как с одной, так и с обеих сторон платы. DIMM (англ. Dual In-line Memory Module, двухсторонний модуль памяти) - форм-фактор модулей памяти DRAM. Данный форм-фактор пришёл на смену форм-фактору SIMM. Основным отличием DIMM от предшественника является то, что контакты, расположенные на разных сторонах модуля являются независимыми, в отличие от SIMM, где симметричные контакты, расположенные на разных сторонах модуля, замкнуты между собой и передают одни и те же сигналы. Кроме того, DIMM имеет 64 (без контроля чётности)или 72 (с контролем по чётности или коду ECC) линии передачи данных, в отличие от SIMM c 32 линиями.

Конструктивно представляет собой длинную прямоугольную плату с рядами контактных площадок вдоль обеих её сторон, устанавливаемую в разъём подключения вертикально и фиксируемый по обоим её торцам защёлками. Микросхемы памяти могут быть размещены как с одной, так и с обеих сторон платы.

В отличие от форм-фактора SIMM, используемого для асинхронной памяти FPM и EDO, форм-фактор DIMM предназначен для памяти типа SDRAM. Изготавливались модули рассчитаные на напряжение питания 3,3 В и (реже) 5 В.

В дальнейшем, в модули DIMM стали упаковывать память типа DDR, DDR II и DDR III, отличающуюся повышенным быстродействием.

Появлению форм-фактора DIMM способствовало появление процессора Pentium, который имел 64-разрядную шину данных. В профессиональных рабочих станциях, таких, как SPARCstation, такой тип памяти использовался с начала 1990-х годов. В компьютерах общего назначения широкий переход на этот тип памяти произошёл в конце 1990-х, примерно во времена процессора Pentium II.

Существуют следующие типы DIMM:

72-pin SO-DIMM (не совместима с 72-pin SIMM) - используется для FPM DRAM и EDO DRAM

100-pin DIMM - используется для принтеров SDRAM

144-pin SO-DIMM - используется для SDR SDRAM

168-pin DIMM - используется для SDR SDRAM (реже для FPM/EDO DRAM в рабочих станциях/серверах)

172-pin MicroDIMM - используется для DDR SDRAM

184-pin DIMM - используется для DDR SDRAM

200-pin SO-DIMM - используется для DDR SDRAM и DDR2 SDRAM

214-pin MicroDIMM - используется для DDR2 SDRAM

204-pin SO-DIMM - используется для DDR3 SDRAM

240-pin DIMM - используется для DDR2 SDRAM, DDR3 SDRAM и FB-DIMM DRAM

Модули памяти типа SDRAM наиболее распространены в виде 168-контактных DIMM-модулей, памяти типа DDR SDRAM - в виде 184-контактных, а модули типа DDR2, DDR3 и FB-DIMM SDRAM - 204-контактных модулей.

Модули RIMM

Модули типа RIMM (Rambus In-line Memory Module) менее распространены, в них выпускается память типа RDRAM. Они представлены 168- и 184-контактными разновидностями, причём на материнской плате такие модули обязательно должны устанавливаться только в парах, в противном случае в пустые разъёмы устанавливаются специальные модули-заглушки (это связано с особенностями конструкции таких модулей). Также существуют 242-контактные PC1066 RDRAM модули RIMM 4200, не совместимые с 184-контактными разъёмами, и уменьшенная версия RIMM - SO-RIMM, которые применяются в портативных устройствах.

Рисунок Модули памяти в различных форм факторах

Рисунок Модули памяти в различных форм факторах

История использовани

я

и основные характеристики

Массовый выпуск SDRAM начался в 1993 году. Первоначально этот тип памяти предлагался в качестве альтернативы для дорогой видеопамяти (VRAM), однако вскоре SDRAM завоевал популярность и стал применяться в качестве ОЗУ, постепенно вытесняя другие типы динамической памяти. Последовавшие затем технологии DDR позволили сделать SDRAM ещё эффективнее. За разработкой DDR SDRAM, последовал стандарт DDR2 SDRAM, а затем и DDR3 SDRAM.

SDR SDRAM

Первый стандарт SDRAM с появлением последующих стандартов стал именоваться SDR (Single Data Rate - в отличие от Double Data Rate). За один такт принималась одна управляющая команда и передавалось одно слово данных. Типичными тактовыми частотами были 66, 100 и 133 МГц. Микросхемы SDRAM выпускались с шинами данных различной ширины (обычно 4, 8 или 16 бит), но как правило, эти микросхемы входили в состав 168-пинного модуля DIMM, который позволял прочитать или записать 64 бита (в варианте без контроля чётности) или 72 бита (с контролем чётности) за один такт.

Использование шины данных в SDRAM оказалось осложнено задержкой в 2 или 3 такта между подачей сигнала чтения и появлением данных на шине данных, тогда как во время записи никакой задержки быть не должно. Потребовалась разработка достаточно сложного контроллера, который не позволял бы использовать шину данных для записи и для чтения в один и тот же момент времени.

Управляющие сигналы

Команды, управляющие модулем памяти SDR SDRAM, подаются на контакты модуля по 7 сигнальным линиям. По одной из них подается тактовый сигнал, передние(нарастающие) фронты которого задают моменты времени, в которые считываются команды управления с остальных 6 командных линий. Имена(в скобках — расшифровки имен) шести командных линий и описания команд приведены ниже:

CKE (clock enable) - при низком уровне сигнала блокируется подача тактового сигнала на микросхему. Команды не обрабатываются, состояние других командных линий игнорируется.

/CS (chip select) - при высоком уровне сигнала все прочие управляющие линии, кроме CKE, игнорируются. Действует как команда NOP (нет оператора).

DQM (data mask) - высокий уровень на этой линии запрещает чтение/запись данных. При одновременно поданной команде записи данные не записываются в DRAM. Присутствие этого сигнала в двух тактах, предшествующих циклу чтения приводит к тому, что данные не считываются из памяти.

/RAS (row address strobe) - несмотря на название, это не строб, а всего лишь один командный бит. Вместе с /CAS и /WE кодирует одну из 8 команд.

/CAS (column address strobe) - несмотря на название, это не строб, а всего лишь один командный бит. Вместе с /RAS и /WE кодирует одну из 8 команд.

/WE (write enable) - Вместе с /RAS и /CAS кодирует одну из 8 команд.

Устройства SDRAM внутренне разделены на 2 или 4 независимых банка памяти. Входы адреса первого и второго банка памяти (BA0 и BA1) определяют, какому банку предназначена текущая команда.